# THE PARALLEL UNIVERSE

# Intel<sup>®</sup> Parallel Studio XE 2013 10 Feature Highlights for Accelerated Performance

by James Reinders

Design

Parallel

Verify

.

Build

reight

\*3/4, bmps/

Layoutkind.Seq

une

### **Boost performance and accuracy**

This downloadable CodeBook provides "how-to" guidance and a comprehensive resource toolkit to help you efficiently produce fast, scalable, reliable applications throughout the development lifecycle.

#### Look for guidance and techniques for C++ and Fortran developers:

Tools and techniques across the development lifecycle

Technical guides, white papers, articles, and blogs

Features for accelerated performance

And much more

$\odot$

#### DOWNLOAD THE FREE CODEBOOK NOW

©2012, Intel Corporation. All rights reserved. Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries \*Other names and brands may be claimed as the property of others.

# CONTENTS

| Letter from the Editor                                                                                                                                                                                                |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Putting Intel <sup>®</sup> Parallel Studio XE 2013 to Work                                                                                                                                                            |   |

| for the "New Normal," BY JAMES REINDERS.                                                                                                                                                                              | 4 |

| Intel <sup>®</sup> Parallel Studio XE 2013:<br>10 Feature Highlights for Accelerated Performance,<br>BY JAMES REINDERS                                                                                                | 6 |

| Get up to speed fast on the components and new feature sets in the Intel® Parallel Studio XE 2013 suite—and consider the potential for your applications.                                                             | U |

| Using Intel <sup>®</sup> Software Development<br>Tools to Analyze HMMER, BY WALTER SHANDS                                                                                                                             | 8 |

| Explore techniques for developing applications like HMMER for the latest generation of multicore processors—from thread and memory error checking to performance and code optimization.                               |   |

| Pointer Checker: Easily Catch Out-of-Bounds                                                                                                                                                                           |   |

| Memory Access, by KITTUR GANESH                                                                                                                                                                                       |   |

| Pointer Checker is designed to catch any out-of-bounds memory accesses before memory<br>corruption occurs. Find out how to use Pointer Checker effectively, and to balance the<br>trade-offs of security and runtime. |   |

| New Parallel Programming Features in                                                                                                                                                                                  |   |

| Intel® (Visual) Fortran Composer XE,                                                                                                                                                                                  |   |

| BY STEVE LIONEL                                                                                                                                                                                                       |   |

| This overview of two new features, DO CONCURRENT and coarrays, brings insight into<br>achieving excellent parallelism results with Fortran.                                                                           |   |

| Using the Intel® Math Kernel Library and Intel® Compiler                                                                                                                                                              |   |

#### Using the Intel<sup>®</sup> Math Kernel Library and Intel<sup>®</sup> complier to Obtain Run-to-Run Numerical Reproducible Results,

#### BY TODD ROSENOUIST AND SHANE STORY.

How do you balance demands for accelerated performance with reproducible results and runtime consistency? These techniques can help you generate reproducible results within applications under a manageable set of constraints.

Sign up for future issues | Share with a friend

© 2012, Intel Corporation. All rights reserved. Intel, the Intel logo, Intel Core, Cilk, VTune, VPro, Xeon and Xeon Phi are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. The Parallel Universe is a free quarterly magazine. Click here to sign up for future issue alerts and to share the magazine with friends.

26

nPsrcdata = getBmpt

James Reinders explores the development capabilities of the mature parallelism tool suite, Intel® Parallel Studio XE 2013.

port("ippi-6.1.dll")) public static extern ippstatus i

coquential,CharSet=CharSet,Ar

new IppiSize( bm

#### LETTER FROM THE EDITOR

### PUTTING INTEL® PARALLEL STUDIO XE 2013 TO WORK FOR THE "NEW NORMAL"

#### Has parallelism changed everything or nothing?

On one hand, parallelism is everywhere and parallel programming is the "new normal." On the other hand, writing, debugging, and tuning an application remains our work to do as programmers. Did we just raise the bar to create the new normal? Perhaps. We expect more from our programming and, in turn, we need more from our tools.

At Intel, we have invested heavily to support this new normal with a wealth of new capabilities in the latest edition of Intel<sup>®</sup> Parallel Studio XE.

The launch of Intel<sup>®</sup> Parallel Studio XE 2013 updates a mature toolset for application development with support we need for the new normal–spanning many aspects of software development.

In this issue, we look at some of the top new features and capabilities of the Intel Parallel Studio XE 2013 product. In the 10 Feature Highlights article, we highlight efforts which are significant new capabilities in their own right. Each could have a whole issue dedicated to it filled with interesting examples and tales on how they work. We've selected three to dive into in this issue beyond the information in the 10 Feature Highlights article. One covers "Pointer Checker," and one discusses Fortran capabilities. Another article covers a new run-to-run (and processor-to-processor) numerical reproducible results capability. This capability helps deal with the inherently non-associative nature of floating point numeric representations with a new unequaled set of options in the latest Intel Parallel Studio XE.

We also have a real-world usage case covered in Using Intel<sup>®</sup> Software Development Tools to Analyze HMMER. This study makes use of event-based sampling analysis in Intel<sup>®</sup> VTune<sup>®</sup> Amplifier XE and the optimization features of the Intel<sup>®</sup> Composer XE compiler to build and analyze hmmsearch and hmmbuild, components of SPECint<sup>\*</sup>.

I think you'll find this issue full of exciting new capabilities. Maybe the end result is a "new normal"—but it is an exciting new place to be.

#### **James Reinders**

Director of Parallel Programming Evangelism at Intel Corporation. James is a co-author of a new book *Structured Parallel Programming* from Morgan Kaufmann, 2012. His other books include *Intel® Threading Building Blocks: Outfitting C++ for Multicore Processor Parallelism*, available in English, Japanese, Chinese, and Korean.

### **Intel<sup>®</sup> Parallel Studio XE 2013:** 10 Feature Highlights for Accelerated Performance

#### by James Reinders, Director of Parallel Programming Evangelism

Intel<sup>®</sup> Parallel Studio XE 2013 not only delivers the latest optimizations and new processor support, but it also includes a number of highly innovative features that are likely to surprise and delight you.

The suite plugs seamlessly into Microsoft Visual Studio\* and the GNU toolchain, thereby preserving investments in your development environment of choice.

1. Processor Support Updated to Include the Latest Intel<sup>®</sup> Processors

New support includes AVX2, TSX, and FMA3. This extends our support to both the newly released 3rd Generation Intel® Core™ vPro™ processor (codenamed Ivy Bridge) microarchitecture, as well as the forthcoming Haswell microarchitecture. This enables you to take advantage of the latest performance enhancements in the newest Intel® products, while preserving compatibility with prior Intel and compatible processors.

#### 2. Support for Intel<sup>®</sup> Many Integrated Core (Intel<sup>®</sup> MIC) Architecture

Used for more than a year on prototype and preproduction systems, support for Intel® MIC architecture is now available in our products. No additional new tools are needed for the first Intel® Xeon Phi™ coprocessor (codenamed Knights Corner). Instead, we have integrated this support in tools you already know and use. The power of these familiar tools is now available to help generate, debug, and optimize code for the Intel® MIC architecture.

#### 3. Advanced Numerical Reproducibility Capabilities

The most praised new feature by beta testers. An innovative new "Conditional Numerical Reproducibility" capability offers unique controls over nonassociative floating-point operations, allowing run-to-run and processor-to-processor reproducibility options often with very low performance penalties. Increased options for floating-point arithmetic reproducibility with Intel® Math Kernel Library, special Intel support in OpenMP\*, and new capabilities in Intel® Threading Building Blocks open up new possibilities.

#### 4. Additional Profiling Data and Easier to Use

Intel<sup>®</sup> VTune<sup>™</sup> Amplifier XE offers new and powerful bandwidth and memory access analysis to reduce time spent puzzling over cryptic performance data.

#### **5. Pointer Checker**

A new compiler-based diagnostic tool allows you to find code that accesses memory addresses beyond the allocated addresses. This helps with security hardening and finding difficult memory corruption issues. With Intel Parallel Studio XE 2013, accelerated application performance is often just a recompilation away. Rebuild with the latest compilers and link in the latest libraries to benefit from the latest processors.

I have chosen 10 features to highlight from this powerful Intel tool suite.

#### 6. New Threading Assistant: Intel® Advisor XE

Intel® Advisor XE assists in producing scalable, maintainable C, C++, C#, and Fortran code. Simplifies adding parallelism to threaded or unthreaded applications, and allows you to evaluate alternatives before investing in implementation.

#### 7. Fortran Standards Support

Intel<sup>®</sup> Fortran supports widely used features of the Fortran 2003 standard and key parts of the 2008 standard, including coarrays. As a leader, Intel is committed to supporting Fortran with our products. Of course, we maintain a rich backward compatibility with decades of Fortran support including VAX Fortran\*, Compaq Visual Fortran\*, Fortran 95, Fortran 90, Fortran 77, and Fortran 66, as well as library support for BLAS, LAPACK, ScaLAPACK, sparse solvers, fast Fourier transforms, vector math, and more.

#### 8.C++ Performance Guide

Everyone can appreciate the new C++ Performance Guide, featuring a quick five-step process for increasing performance.

#### 9. C and C++ Standards Support

Outstanding support for C and C++ are now accompanied by leading support for many of the new C++11 and C11 features. We also maintain our extensive support for prior standards including C99, and industry-leading support for IEEE 754-2008 Decimal Floating-Point Arithmetic.

#### 10. Find and Eliminate Errors with Intel® Inspector XE

Intel® Inspector XE provides an efficient way to increase your application reliability to ensure performance in C, C++, C#, and Fortran. The new heap growth analysis feature offers an important new way to find memory leaks.

DOWNLOAD A FREE 30-DAY EVALUATION

### The power of this suite stems from four key components:

#### 1. Optimized C++ and Fortran Compilers and Libraries:

Intel® Composer XE is a highly optimizing performance-oriented developer tool that includes Intel® C++ and Fortran compilers, and threading, math, multimedia, and signal processing performance libraries. Intel® Cilk™ Plus, Intel® Threading Building Blocks, and OpenMP\* support provide parallelism models to make it easier to take advantage of today's and tomorrow's high-performance computing systems. Industry-leading Intel® Math Kernel Library and Intel® Integrated Performance Primitives include a wealth of routines to improve performance and reduce development time.

#### 2. Innovative Threading Assistant for Linux\* and Windows\*:

Intel® Advisor XE is a threading assistant for C, C++, C#, and Fortran developers. It helps find regions with the greatest performance potential from parallelism and highlights critical synchronization issues. With Advisor XE, you can evaluate alternatives before investing in implementation, estimate the speed-up, identify correctness issues and select the options with the best return on investment. The "magic" here is in the ability to evaluate approaches before committing to coding and debugging. This is a remarkable tool when considering how to add parallelism into your code.

- 3. Optimize Serial and Parallel Performance: Intel® VTune™ Amplifier XE is the premier performance and thread profiler to tune application performance. Use it to profile C, C++, C#, Fortran, assembly code, and Java code, and receive rich performance data for hotspots, threading, locks and waits, DirectX\*, bandwidth, and more.

- 4. Deliver More Reliable Applications: Intel® Inspector XE 2013 is an easy-to-use memory and threading error detector for serial and parallel applications on Windows\* and Linux\* Static analysis for C, C++, and Fortran developers is included in Intel® Studio XE products. The ability to pinpoint active and latent problems before shipping an application to customers is strongly supported by this acclaimed and unique Intel capability. □

TO LEARN MORE, VISIT

#### **TECHNICAL SPECIFICATIONS AT A GLANCE**

| Processor Support                     | Validated for use with multiple generations<br>of Intel and compatible processors<br>including, but not limited to: Intel® Xeon®<br>processors, Intel® Core® processors, and<br>Intel® Xeon Phi® coprocessors.                                              |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Systems                     | Windows* and Linux*. Compiler and<br>library components are also available as<br>Apple OS* X add-ons for Apple's XCode*<br>development environment.                                                                                                         |

| Development Tools<br>and Environments | Compatible with compilers from vendors<br>that follow platform standards (e.g.,<br>Microsoft, GNU, Intel). Can be integrated<br>with GNU toolchain; Microsoft Visual<br>Studio* 2008, and 2010, and next-<br>generation tools.                              |

| Programming<br>Languages              | Extensive support for C, C++ and Fortran<br>development. Additional support included<br>for programs that also include Java or<br>.NET languages such as C#.                                                                                                |

| Support                               | All product updates, Intel® Premier<br>Support services, and Intel® Support Forums<br>are included for one year. Intel Premier<br>Support gives you access to confidential<br>support, technical notes, application notes,<br>and the latest documentation. |

| Community                             | Join the Intel <sup>®</sup> Support Forums community to learn, contribute, or just browse: http://software.intel.com/en-us/forums                                                                                                                           |

| System<br>Requirements                | For details on hardware and software<br>requirements:<br>www.intel.com/software/products/<br>systemrequirements/                                                                                                                                            |

by Walter Shands, Software Development Engineer

# Using Intel® Software Development Tools to Analyze HMMER

This paper will highlight the features of Intel® Parallel Studio XE 2013 by using them to build and analyze HMMER (http://hmmer.janelia.org/). HMMER is a set of applications, which includes two, hmmsearch and hmmbuild, which are components of SPECint. We make use of eventbased sampling analysis in Intel® VTune" Amplifier XE to find out which code paths, context switches, or threading inactivity cause performance problems in hmmsearch. And, we'll utilize the code optimization features of the Intel® Composer XE compiler to improve the performance of hmmsearch on Intel® Xeon® E5 processors. In addition, we will show you how to use Intel® Inspector XE to locate memory and threading errors introduced into hmmsearch. **hmmsearch is used to search** a protein sequence database for homologs of protein sequences using profiles called hidden Markov models. globins4.hmm contains the profiles and uniprot\_trembl.fasta is a 10 GB sequence database.

hmmsearch is available in an MPI version, but we restricted our experiments to the non-MPI flavor. We ran hmmsearch on a computer with an 8-core Intel® Xeon® E5-2680 hyperthreaded processor at 2.7 GHz with 23.4 GB of memory. We ran the application using GCC and the Intel® C compiler, in both cases using the settings provided by the configure script. The initial GCC default switches were:

> gcc -std=gnu99 -O3 -fomit-frame-pointer -malign-double -fstrict-aliasing -pthread -msse2

The application requires support for the SSE2 instruction set at a minimum to support an algorithm optimized using intrinsics oriented toward SSE2.

The default Intel® compiler flags were:

#### icc -03 -ansi\_alias -pthread

A challenge in porting applications from one compiler to another is making sure that there is support for the compiler options you use to build your application. The Intel C compiler supports many of the options that are valid on other compilers you may be using, such as GCC. The compiler generates object files that are compatible with GCC-generated object files, so you can compile part of your application using the Intel compiler and the rest using GCC.

The **-fomit-frame-pointer** option is set when you specify option **-O1**, **-O2**, or **-O3** when using the Intel C compiler (so there is no need to include it). The -malign-double option aligns double, long- double, and long-long types for better performance for systems based on IA-32 architecture and is available in the Intel C compiler.

We started the application with this command line:

./hmmsearch globins4.hmm ../../

uniprot\_trembl.fasta

The next step is to locate the hotspots in the application using Intel VTune Amplifier XE. This profiler tool uses low overhead techniques to quickly find multicore performance bottlenecks, without needing to know the processor architecture or assembly code. Note that we do not need to add code to the application to collect data.

To view source code lines of hmmsearch in VTune Amplifier XE, we need to include symbols in the release build—so we add the **\_g** flag. We added the **\_fno\_inline\_functions** flag as well; this allows us to see all of the code in question in the VTune Amplifier XE source view.

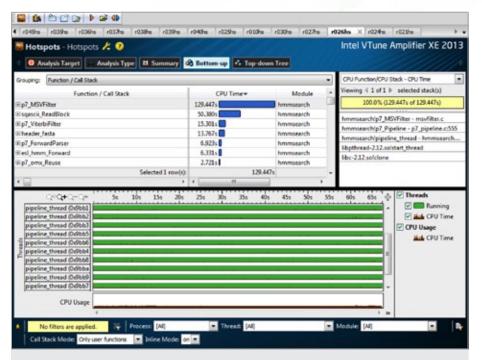

The VTune Analyzer XE hotspots analysis shows where most of the CPU activity is occurring in the application and the amount of CPU activity on the threads over time. (Figure 1)

The VTune Amplifier XE hotspots view tells us that the function consuming the most CPU time is p7\_MSVFilter, and double-clicking on the function name displays the SSE intrinsics calls used in optimizing the performance of the function. The assembly view shows us that the Intel compiler utilized vector instructions, but is not taking advantage of the 256-bit registers or AVX instructions on the Intel Xeon processor. (Figure 2)

It's possible that we could compile the original C code for p7\_ MSVFilter with the Intel compiler and help the compiler vectorize the function for the instruction set available on the target machine, so that the function is not limited to using 128 bit registers.

The thread timeline view shows that there is not much CPU time used in the worker threads, but a large amount is used in one thread. This turns out to be the thread that is reading the sequence database file. (Figure 3)

"To achieve more significant performance gains, the problem of serialization of the application due to the file read has to be solved."

Figure 1

| Source | Assembly   |           | 1.20 - | 0 9      | 8    |                        |        | CPU time                                 |

|--------|------------|-----------|--------|----------|------|------------------------|--------|------------------------------------------|

| Line   | Source     | Second a  | c^_    | Address  | Line | Assembly               | CPU 1  | 1 stack(s) selected. Viewing = 1 of 1 =  |

| 146    | sv =       | mn_add    | 4      | 0x42ffc9 | 147  | vpsubusbx (%r15), %xmm | 9.488  | Current stack is 100.0% of selection     |

| 147    | SV =       | mn sut    | 25     | 8x42ffce | 147  | add \$0x10, %r15       | 20.201 | 100.0% (129.447s of 129.447s)            |

| 148    | xEv =      | 80 83X    | 0      | 0x42ffd2 | 150  | vmovdqux (%rbx), %xms8 | 5.710  | hmmsearch1p7_MSVFilter - msvfilter.c     |

| 149    |            |           |        | 0x42ffd6 | 148  | vpmaxub %xmml1, %xmml, | 0.120  | hmmsearch/p7_Pipeline - p7_pipeline.c:5  |

|        | Selected 1 | I row(s): | 29     |          |      | Highlighted 2 row(s):  | 29.68  | hmmsearchipipeline thread - hmmsearc     |

| 6      |            | 3         | 6 2    |          |      | - HI                   | 1 10 2 | libothread-2.12 solstart_thread+0xd0 - [ |

#### Figure 2

Figure 3

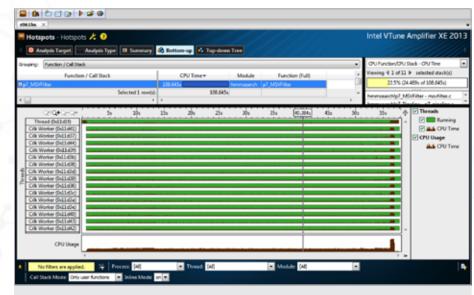

The application creates a number of threads equal to the number of HW threads on the machine plus one, which in the case of a hyperthreaded machine is equal to the number of hyperthreads plus one. In this case, there are 17 threads running. If we use the hmmsearch -cpu 4 flag to limit the threads to five threads, VTune Amplifier XE shows that the application scales well–unlike the situation with 17 threads. (Figure 4)

Evidence of this is the 67.418-second runtime with 17 threads, which is worse than the 62.561-second runtime with four threads.

We can see that the top thread is the one reading the data file by filtering the results by thread in the five-thread hotspot display. (Figure 5)

|                                                                                                                                                                                                                                      | r040hs r025hs r030hs                                                                                                                                                                                                                    | r030hs r027hs ×                                                                                                                                        | r026/m r024/m r025/m ) •                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Motspots - Hotspots 2 🖉                                                                                                                                                                                                              |                                                                                                                                                                                                                                         |                                                                                                                                                        | Intel VTune Amplifier XE 2013                                                                                                                                                                                  |

| Grouping: Punction / Call Stack<br>Function / Call Stack                                                                                                                                                                             | CPU Time*                                                                                                                                                                                                                               | •<br>Module                                                                                                                                            | CPU Function/CPU Stack - CPU Time  Viewing 4 1 of 1  selected stack(s)                                                                                                                                         |

| tr p?_JSVFilter<br>Bisgarcti, ReadBock<br>Bip7,Veetbilter<br>Bihaader, fasta<br>Bied, herm, Forward<br>Hip7, ForwardParser<br>Biloadbud<br>Bip7, oms, Reuse<br>Bilogf<br>Biesp<br>Biesp<br>Biogf<br>Biesp<br>Selected 1 row(u):<br>4 | 131.313           47.093           14.751           11.311           6.381.8           6.130.6           2.571.8           2.5995           1.9995           1.1405           0.751.           1.1405           0.751.           1.14.3 | Immisearch<br>Immisearch<br>Immisearch<br>Immisearch<br>Immisearch<br>Immisearch<br>Immisearch<br>Immisearch<br>Immisearch<br>Immisearch<br>Immisearch | 100.0% (131.333) of 131.313)<br>hmmsearch(p7_MSVFilter - msvfilter.c<br>hmmsearch(p7_Fipeline - p7_pipeline.c535<br>hmmsearch(pipeline_thread - hmmsearch<br>libpthread-121.schtart_thread<br>libc-212.aoldone |

| CPU Usage                                                                                                                                                                                                                            | s 25s 30s 35s<br>▼ Threa⊈ [44]                                                                                                                                                                                                          | 40s 45s 50s                                                                                                                                            | 55s 60s<br>♥ Threads<br>♥ Running<br>♥ CPU Usage<br>♥ CPU Usage<br>↓<br>►<br>►<br>►<br>►<br>►<br>►<br>►<br>►<br>►<br>►<br>►<br>►<br>►                                                                          |

Figure 4

#### 📓 🕼 🖄 🖄 🕼 🕼 🕼 🕼 r050hs r042hs r049hs r038hs r039hs r040hs r029hs r010hs r030hs r027hs X r035ha r036hs 10176 Intel VTune Amplifier XE 2013 Hotspots - Hotspots 🔏 🥹 Analysis Type 🛛 Summ. up 📫 Top-down Tree Analysis Target Botte PU Function/CPU Stack - CPU Time Thread / Function / Call Stack . g 4 1 of 13 > selected stack(s) Thread / Function / Call Stack CPU Time 76.7% (47.093s of 61.394s) 47.093 III sqascii ReadBl search/sgascii\_ReadBlock - esl\_sgio\_as B header\_fasta 11.311s wearchiesl\_sqio\_ReadBlock - esl\_sqio.c. **H** loadbuf 2.571: hmmsear\_ earchiserial\_master - hmmsearch.c451 0.150 Best\_sq\_GrowTo hmmsear... searchimain - hm tearch c:289 R pthread\_cond\_broadcast 0.100 bothres\_ search/\_start end\_fasta 0.080 III p7\_alidisplay\_Print 0.030 E est\_sgio\_IsAlignment 0.030 sear Bp7\_tophits\_Domains 0.010 Maktado 0.010 Selected 1 ro 61.394 Thread Q# ad (D) CPU Time ne\_thread () CPU Usage thread (Dy9e19 HA CPU Time e\_thread (0. CPU Usage Thread (Al) Module: [Al Process: [Al Call Stack Mode Inline Model

Figure 5

12

For more information regarding performance and optimization choices in Intel<sup>®</sup> software products, visit http://software.intel.com/en-us/articles/optimization-notice

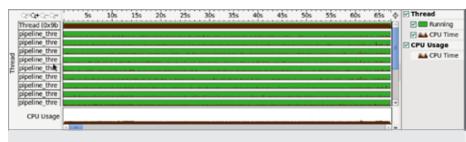

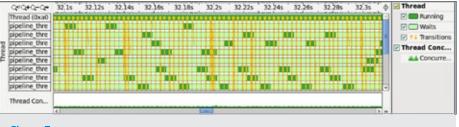

If we use the VTune Amplifier XE Locks and Waits feature on the run with 17 threads it shows us a large number of transitions, indicated by yellow lines from the thread reading the sequence database file to worker threads. (Figure 6)

hmmsearch uses a producer consumer model. This is where a producer thread (labeled Thread (0xa0) in the graphic) puts data to be processed on a queue that worker threads (labeled pipline\_thread in the graphic) remove when the producer thread signals them with a broadcast message, resulting in a thread transition from the producer thread to the worker thread.

By zooming in, we can see that the amount of thread running time (dark green) is less than thread waiting time (light green), indicating lost time to do productive work. (Figure 7)

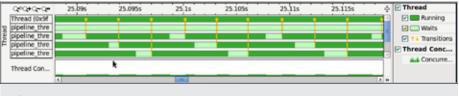

Compare this with a zoom-in on the thread view for hmmsearch using only four threads. Note that thread transitions from the thread reading the data file, the top thread, typically result in productive work to the worker thread. (Figure 8)

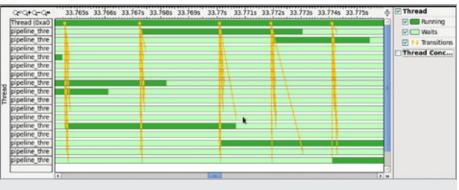

However, when using 17 threads in hmmsearch, many thread transitions do not result in work being done. (**Figure 9**)

Zooming in even closer on the 17 thread case, we can see these thread transitions are the result of a pthread\_cond\_broadcast call that tells the worker threads that a block of data is ready on the work queue to be processed. Only one thread at time can grab the block of data—so the

other threads must wait again. (Figure 10)

When only five threads are used, only about two threads are waiting to get a block of data to process, and only one thread goes unsatisfied. (**Figure 11**)

All of this indicates that with more than four threads, the hmmsearch pipeline threads become starved for data. In other words, the thread reading the data file cannot provide data fast enough to keep up with computation in the worker threads.

From our analysis using VTune Amplifier XE, we know that the most time-consuming code is the MSV algorithm, which has been optimized with SSE intrinisics in p7\_ MSVFilter in the file msvfilter.c. The intrinsic-optimized code also contains some optimizations over and above vectorization, so it will be faster.

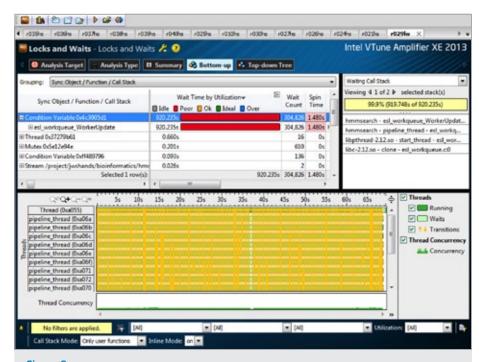

To see if the Intel compiler can effectively vectorize the nonintrinsic optimized code, we compiled the application to use the unoptimized C code in the function p7\_GMSV in the file generic\_msv.c. VTune Amplifier XE again shows that the MSV algorithm is the hotspot. (Figure 12)

VTune Amplifier XE also shows that the most time-consuming part of the MSV algorithm is a single loop that is not taking advantage of AVX instructions or YMM registers on the Intel Xeon processor. (Figure 13)

The runtime of hmmsearch using this code is about four minutes and 30 seconds.

```

# CPU time: 4137.39u 5.02s

01:09:02.41 Elapsed: 00:04:30.08

```

If we use the –opt-report flag for the Intel compiler, it will tell us what inlining, loop, memory, vectorization, and parallelization optimizations have been done for each function. For the p7GMSV function, it tells us the loop was not vectorized.

generic\_msv.c(80:7-80:7):VEC:p7\_GMSV: loop

was not vectorized: existence of vector

dependence

By restructuring the code, we can enable the compiler to vectorize the loop and generate code that takes advantage of Intel Xeon architecture. The optimization report from the compiler indicates that the two loops resulting from the restructuring were vectorized:

generic\_msv.c(88:7-88:7):VEC:p7\_

GMSV: LOOP WAS VECTORIZED

```

generic_msv.c(108:7-108:7):VEC:p7_

GMSV: LOOP WAS VECTORIZED

```

In addition, the VTune Amplifier XE assembly view shows that AVX instructions are being used along with the larger YMM registers. (Figure 14)

#### The resulting runtime of the application is close to half of the

original runtime.

5

```

# CPU time: 2207.74u 4.96s

00:36:52.69 Elapsed: 00:02:28.16

```

We can use Intel Inspector XE to check hmmsearch for threading and memory errors. It gives detailed insight into application memory and threading behavior to improve application reliability, and its powerful thread checker and debugger make it easier to find latent errors on the executed code path. Intel Inspector XE also finds intermittent and nondeterministic errors, even if the error-causing timing scenario does not happen.

| Thread (0xa0            | <b>\$</b> |                                                             | 🛛 🖾 Running | Figure 10 |  |

|-------------------------|-----------|-------------------------------------------------------------|-------------|-----------|--|

| pipeline_thre           |           |                                                             | V Waits     |           |  |

| sipeline_thre           |           |                                                             | Transitions |           |  |

| sipeline_thre           |           |                                                             | Thread Conc |           |  |

| pipeline_thre           |           |                                                             | Inread Conc |           |  |

| pipeline_thre           |           | Transitions                                                 |             |           |  |

| sipeline_thre           |           | Thread (0xa055) to pipeline_thread (0xa074) (33.770s to 33. | 771s)       |           |  |

| sipeline thre           |           | Sync Object: Condition Variable 0x4c3005d1                  |             |           |  |

| pipeline_thre           |           | Source File: esl_workqueue.c                                |             |           |  |

| vipeline_thre           |           | Source Line: 395                                            |             |           |  |

| sipeline_thre           |           | Signal Source File: esl_workqueue.c                         |             |           |  |

| sipeline thre           |           | Signal Source Line: 312                                     |             |           |  |

| speline_thre            | i ii      | Whiting                                                     |             |           |  |

| pipeline_thre           |           | Waiting<br>Start: 33.770s Duration: 1.817ms                 |             |           |  |

| pipeline thre           | 100       | Sync Object: Condition Variable 0x4c3005d1                  |             |           |  |

| sipeline thre           |           | Source File: esl_workqueue.c                                |             |           |  |

| sipeline thre           |           | Source Line: 395                                            |             |           |  |

|                         |           | Signal Source File: esl_workqueue.c                         |             |           |  |

| ٤                       |           | Signal Source Line: 312                                     |             |           |  |

| to filters are applied. |           | ode: on V Call Stack Mode: Only user                        |             |           |  |

| Grouping: Sync                                  | Object / Function / Call Stack |              |              |         | ~         | Object Creation 🗸                                                                                                                                                                                                                                                                                                                                          | Figure 11 |

|-------------------------------------------------|--------------------------------|--------------|--------------|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                 | 1                              | Wait<br>Cou. | Spin<br>Time | Module  | Objec     | 1 stack(s) selected. Viewing ⊲ 1 of 1 ▷<br>CL Transitions<br>Thread (0x9f70) to pipeline_thread (0x9f86) (25.103s to 25.103s)                                                                                                                                                                                                                              |           |

| Condition Variab                                | ble 0x4c3005d1                 | 38           | Oms          |         | Condition | Sync Object: Condition Variable 0x4c3005d1                                                                                                                                                                                                                                                                                                                 |           |

| V Mutex 0x5e12es                                | Selected 1 row(s):             | 38           | 0ms<br>0ms   | 25.1029 | Mutex     | hmm Source File: esl_workqueue.c<br>hmm Source Line: 395<br>Signal Source File: esl_workqueue.c<br>Signal Source Line: 312<br>hmm<br>Waiting<br>Start: 25.100s Duration: 2.965ms<br>Sync Object: Condition Variable 0x4c3005d1<br>Source File: esl_workqueue.c<br>Source Line: 395<br>Signal Source File: esl_workqueue.c<br>25.11 Signal Source File: 312 |           |

| Thread (0x9f                                    |                                |              |              |         |           | N Maring                                                                                                                                                                                                                                                                                                                                                   |           |

| pipeline_thre<br>pipeline_thre<br>pipeline_thre |                                |              |              |         |           | Waits                                                                                                                                                                                                                                                                                                                                                      |           |

| E pipeline_thre                                 |                                |              |              |         |           |                                                                                                                                                                                                                                                                                                                                                            |           |

| pipeline_thre                                   |                                |              |              |         |           | ☑ Thread Conc                                                                                                                                                                                                                                                                                                                                              |           |

| Thread Con                                      |                                |              |              |         |           | Concurre                                                                                                                                                                                                                                                                                                                                                   |           |

|                                                 |                                | _            |              |         |           |                                                                                                                                                                                                                                                                                                                                                            |           |

"The Intel® C compiler and libraries create faster code, Intel® VTune® Amplifier XE finds bottlenecks, and Intel® Inspector XE pinpoints memory and threading errors before they happen. All this is of critical importance when developing applications like HMMER."

#### 🗳 🕼 🖄 🖆 🕞 🕨 🗳 🕪 r050he r042he r049he r039he r039he r039he r039he r039he r040he × r064pe Intel VTune Amplifier XE 2013 Hotspots - Hotspots 🦧 📀 alysis Type 🛛 Summary 🚳 Bottom-up 🔹 Top-down Tree is Target A PU Function/CPU Stack - CPU Time a 4 1 of 2 > selected stack(s) Function / Call Staci CPU Time\* Module Function (Fu 99.9% (472.987s of 473.677s p7\_MSVFilter + p7\_Pipeline + pip 473.6779 nsearch p7\_GMSV mmsearchlp7\_GMSV - generic\_msv.c GViterb 22.401s nsearch p7\_GViterbi nmuearch/p7\_MSVFilter - muvfilter.c:56 of Floom 0.800+ immsearch p7\_FLogsum search/p7\_Pipeline - p7\_pipeline.c555 addbuf 3.782s mmsearch addbuf ip7\_GForward mmsearch p7\_GForward 2.157 2148+ mmsearch seebuf netchar 1.1824 mmsearch nextcha header\_fasta 0.8271 hmmsearch header\_fasta p7\_gmx\_GrowTo 0.757s mmsearch p7\_gmx\_GrowTo 0.720 Selected 1 row(s) 473.6775 Q+ 10. 156 201 2 - Ru 10,171,c2 CPU Time CPU Usage AL CPU Time CPU UN Thread: [A] Module [A]

#### Figure 12

|      | Assembly 🔳 🖽 🗔      | 0 49 49 1             | 8          |      |                                        |          |    |

|------|---------------------|-----------------------|------------|------|----------------------------------------|----------|----|

| Une  | Source              | CPU Time              | Address    | Line | Assembly                               | CPU Time |    |

| 79   |                     | and the second second | ∎ 0x4259cc | 82   | vmaxss %xmm7, %xmm6, %xmm6             | 0.1205   |    |

| 80   | for (k = 1; k <= gr | 29.4445               | 0x4259d0   | 82   | vaddssl 0x8(%rcx,%rdx,4), %xmm6, %xmm9 | 1.0915   |    |

| 81   | (                   |                       | 8x4259d6   | 82   | vmovssl %xmm9, 0xc(%r12,%rsi,4)        | 25.8895  |    |

| 82   | MRK(1,k) = MSC(     | 232.5386              | 0x4259dd   | 83   | vmovssl 0x14(%r14,%r11,4), %xmm8       | 0.4095   | 12 |

| 83   | XMX(1,p7G_E) = ESL  | 206.038s              | 0x4259e4   | 83   | vnaxss txmm9, txmm8, txmm8             | 25.0365  |    |

| 84   | )                   |                       | 0x4259e9   | 82   | vaddssl 0xc(%r14,%r11,4), %xmm1, %xmm1 | 99.663s  |    |

| 85   |                     |                       | 0x4259f0   | 83   | vmovssl %xmm8, 0x14(%r14,%r11,4)       | 0.1725   | 1  |

| 86 / |                     |                       | 8x4259f7   | 82   | vmovssl 0xc(%r15,%rsi,4), %xmm10       | 27.1275  |    |

| 87   | for (k = 1; k <= gt |                       | 0x4259fe   | 82   | vmaxss %xmm11, %xmm10, %xmm10          | 0.1605   |    |

| 88   | (                   |                       | 0x425a03   | 82   | vaddssl 0x10(%rcx,%rdx,4), %xmm10, %xm | 0.0905   |    |

| 89   | if (MMX(1-1,k-1) >  |                       | 0x425a09   | 82   | vmovssl %xmm13, 0x18(%r12,%rsi,4)      | 25.5485  |    |

Intel Inspector XE finds memory leaks, corruption, and inconsistent memory API usage, as well as data races, deadlocks, and memory accesses between threads.

As with Intel VTune Amplifier XE, we don't need to create a special build or add code to the application to collect data.

Because there is significant overhead in detecting memory and threading bugs, we launch hmmsearch using a smaller sequence database file, as well as an application option that reduces the number of threads.

When we run Intel Inspector XE in the Detect Memory Problems mode, a few uninitialized memory accesses are exposed. (Figure 15)

Right-clicking on a line in the Detect Memory Problems pane brings up a description of an uninitialized memory access problem: (Figure 16)

Intel Inspector XE running in Locate Deadlocks and Data Races mode did not detect any issues. (Figure 17)

In order to increase application performance, we can take advantage of Intel<sup>®</sup> Cilk<sup>®</sup> Plus in the Intel compiler. Cilk Plus is an extension to C and C++ that offers a quick, easy, and reliable way to improve the performance of programs on multicore processors. It is an open standard and will soon be available in GCC 4.7. Cilk Plus, included in the Intel<sup>®</sup> C/C++ compiler, allows you to improve performance by adding parallelism to new or existing C or C++ programs using only three keywords: cilk\_for, cilk\_ spawn, and cilk sync.

Analysis Target Analysis Type 🖩 Collection Log 👖 Summary 📣 Bottom-up 🐟 Top-down Tree 🔝 generic - - -CPU Tim **CPU Time** Address Line Line Source Assembly 4.8455 vinsertf128 \$0x1, %xmm11, %ymm10, %ym XPO((1,p76 E) = ESL MAX(XP 0x425a56 84 93 85 0x425a5c 93 vaddps tymm12, tymm2, tymm2 0.6805 86 •/ 0x425a61 vextractf128 \$0x1, %ymm2, %xmm13 8.6125 91 vmovssl %xmm2, 0xc(%r14,%r12,1) vextractpsl \$0x1, %xmm2, 0x18(%r14,%r 87 0x425a67 4.5205 91 for (k = 1; k <= gn->H; k 9.126s 88 0x425a6e 91 0.500s vext/sctpsl \$0x2, %xmm2, 0x24(%r14,%r 0x425a76 8.007s 89 91 1f (MMCK(1-1,k-1) > (XMCK(1 vextractps1 \$0x3, %xmm2, 0x30(%r14,%r 50 55.4525 0x425a7e 4.3475 91 0x425a86 91 vmovssl %xmm13, 0x3c(%r14,%r12,1) 4.7195 62 else Brd25a84 91 vextractpsl \$0x1, %xmm13, 0x48(%r14,% 5.1856 MMX(1,k) = MSC(k) + XMX 93 74.768s 0x425a95 91 vextractosl \$0x2, %xmm13, 0x54(%r14,% 4.6945 91 vextractpsl \$0x3, %xmm13, 0x60(%r14,% Highlighted 25 row(s): 0x425a9d 4.7165 54 Selected 1 row(s): 109.4415

#### Figure 14

| _     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                               |                               |           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|-------------------------------|-----------|

| r024n | ml3 🛞 //034mi3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |                               |                               |           |

| ۳. μ  | ocate Memory Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |                               | Intel Inspec                  | tor groza |

| -     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ummary              |                               |                               | 0103      |

| Probl | and the second se | enninar y           | © Filter                      | 3                             | Sort -    |

| D.    | Problem Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Modules Object Si   | State Seve                    | rity                          |           |

| 4 1   | Uninitialized memory access p7_trace.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hmmse               | New Error                     |                               | 9 item(s) |

| 5 1   | Uninitialized partial memor esl_sq.c; p7_alidi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | hmmse               | New Prob                      | lem                           |           |

| 6 1   | O Uninitialized partial memor p7_oprofile.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | hmmse               |                               | d partial memory access       | 2 item(s  |

| 7 1   | Uninitialized partial memor p7_tophits.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | hmmse               | ALC: NOT THE REAL PROPERTY OF | ory leak                      | 1 item(s  |

| Code  | Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | de Locations / Time | line © Uninit                 | dalized memory access         | 2 item(s  |

| DD    | Ascription Source Function Mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | dule Object Size    | Offset Uninit                 | salized partial memory access | 4 item(s  |

| X A   | illocation site 🖹 esl_sq.c:1732 sq_init hm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | msea                | Sour                          | ce                            |           |

| 173   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1993-9419           | easel                         | c.                            | 2 item(s  |

| 171   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | esl_s                         |                               | 1 item(s  |

| 173   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | hmm                           | search.c                      | 1 item(s  |

| 173   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                               | display.c                     | 2 item(s  |

| XB    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | p7_hr                         | nm.c                          | 1 item(s  |

| 195   | and the second of the building of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | += hmm p7_op                  | rofile.c                      | 1 item(s  |

| 96    | sg namelen = strlen(sg->name);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     | = sq n p7_to                  | phits.c                       | 2 item(s  |

| 97    | <pre>sq acclen = strlen(sq-&gt;acc);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | - sq a p7_tr                  | sce.c                         | 2 item(s  |

| 98    | <pre>sq_desclen = strlen(sq-&gt;desc);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n                   | += sq_d Modu                  | ile.                          |           |

| 99    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                               | search                        | 9 item(s  |

#### Figure 15

Help: Uninitialized Partial Memory Access

#### Uninitialized Partial Memory Access

Occurs when a read instruction references a block (2-bytes or more) of memory where part of the block is uninitialized.

| ID | Code Location                                                                      | Description                                                                                                                                  |

|----|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Allocation site                                                                    | If present, represents the location and associated call stack from which the memory block<br>containing the offending address was allocated. |

| 2  | Read                                                                               | Represents the instruction and associated call stack responsible for the partial uninitialized<br>access.                                    |

|    |                                                                                    | If no allocation or deallocation is associated with this problem, the memory address might be i<br>stack space.                              |

| un | person<br>signed char age;<br>ar firstInital;<br>ar middeInital;<br>ar lastInital; |                                                                                                                                              |

| Ele View Help                                                                                                                                                                                                                       |                                                                                |                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------|

| r024mi3 r034mi3 r035t/3 x                                                                                                                                                                                                           |                                                                                |                                |

| Locate Deadlocks and Data Races O Target Analysis Type R Collection Log Summary                                                                                                                                                     |                                                                                | Intel Inspector 024m<br>07034m |

| Problems                                                                                                                                                                                                                            | 2 Filters                                                                      | Sort + C                       |

| No Problems Detected<br>Intel Inspector XE 2011 detected no problems at this analysis scope. If this result is<br>unexpected, try rerunning the target using an analysis type with a wider scope. Press<br>F1 for more information. | Severity<br>Problem<br>Source<br>Module<br>State<br>Suppressed<br>Investigated |                                |

#### Figure 17

We use Cilk Plus to replace the code that manages threads, mutexes, condition variables, and the work queue with the added benefit of better scheduling. However, we must still synchronize threads on the data file read, which results in serializing a portion of the application.

In the Intel VTune Amplifier XE Hotspots graphic of an hmmsearch run, you can see that because of the synchronization resulting from mutexes around the code reading the sequence database file, the CPUs are not fully utilized. But the Cilk Plus implementation has a shorter runtime at 58.272 seconds compared to the original runtime of 67.418 seconds. (Figure 18)

If we run a VTune Amplifier XE locks and waits analysis we can see that there are still many thread transitions. (Figure 19)

If we zoom into the thread pane in the locks and waits analysis, we see that the thread transitions are between worker threads, and that they involve the mutex that protects the file read, which is now carried out by each worker thread. (Figure 20)

#### Figure 18

|    | Q#Q#Q=Q#              | 15.165                              | 15.185 | 15.25               | 15.225                          | 15.215.25075s26s               | 15.285     | 15.35                   | \$    | Thread              |

|----|-----------------------|-------------------------------------|--------|---------------------|---------------------------------|--------------------------------|------------|-------------------------|-------|---------------------|

|    | Thread (0x11e18)      | and the second second second second |        | doorst vonderstaten | and a section of the section of |                                |            | denter released and     | - T   | Running             |

|    | Cilk Worker (0x11e33) |                                     |        |                     |                                 |                                |            |                         |       | P Waits             |

|    | Cilk Worker (0x11e3d) |                                     |        |                     | - 11                            |                                |            |                         |       | PI 14 Transitions   |

|    | Cilk Worker (0x11e34) |                                     |        |                     |                                 |                                |            |                         |       |                     |

|    | Cilk Worker (0x11e31) |                                     |        |                     |                                 |                                |            |                         |       | Thread Conc         |

|    | Cilk Worker (0x11e35) |                                     |        | 6 i i f             |                                 |                                |            |                         |       | AL Concurre.        |

|    | Cilk Worker (0x11e3b) | -                                   | 411    |                     |                                 | -                              |            |                         |       |                     |

| 8  | Cilk Worker (0x11e30) |                                     |        |                     |                                 | Transitions                    |            | and some drawn and some |       |                     |

| ٤. | Cilk Worker (0x11e38) |                                     |        |                     |                                 | Sync Object:                   |            |                         | 11630 | (15.251s to 15.251s |

| F  | Cilk Worker (0x11e32) | -                                   |        |                     |                                 | Source File: h                 |            | 69193                   |       |                     |

|    | Cilk Worker (0x11e2f) |                                     |        |                     | 1.000                           | Source Line: 1                 |            |                         |       |                     |

|    | Cilk Worker (0x11e3c) | 6                                   | - 11   |                     | 1 1 1                           | Signal Source                  |            | arch.c                  |       |                     |

|    | Cilk Worker (0x11e37) |                                     | - 11   |                     | 16 111                          | Signal Source                  |            |                         |       |                     |

|    | Cilk Worker (0x11e36) |                                     |        |                     |                                 |                                |            |                         |       |                     |

|    | Cilk Worker (0x11e39) |                                     | - 14   |                     |                                 | Waiting                        |            |                         |       |                     |

|    | Cilk Worker (0x11e3a) |                                     |        |                     |                                 | Start: 15.205                  |            |                         |       |                     |

|    |                       |                                     |        |                     |                                 | Sync Object:                   |            | :5/93                   |       |                     |

|    |                       | 1.1                                 |        |                     |                                 | Source File: h<br>Source Line: |            |                         |       |                     |

|    | Thread Concurrency    |                                     |        |                     |                                 | Signal Source                  |            | arch e                  |       |                     |

|    |                       |                                     | _      | -                   |                                 |                                | Line: 1542 | art from the            |       |                     |

#### Figure 20

#### S (100) > S (10)