## The Present and Future of OpenMP\*

How the Gold Standard Parallel Programming Language Has Improved

Improve Performance on Multicore and Many-Core Intel® Architectures

Identify Scalability Problems in Parallel Applications

0111000<sup>1</sup> 0111001<sup>1</sup> 0111010<sup>1</sup>

## **CONTENTS**

| Letter from the Editor The Changing HPC Landscape Still Looks the Same by Henry A. Gabb, <i>Principal Engineer</i> at Intel Corporation                                              | 3  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| The Present and Future of the OpenMP* API Specification  How the Gold Standard Parallel Programming Language Has Improved with Each New Version                                      | 5  |

| Reducing Packing Overhead in Matrix-Matrix Multiplication Improve Performance on Multicore and Many-Core Intel® Architectures, Particularly for Deep Neural Networks                 | 21 |

| Identify Scalability Problems in Parallel Applications  How to Improve Scalability for Intel® Xeon and Intel® Xeon Phi™ Processors Using New Intel® VTune™ Amplifier Memory Analysis | 26 |

| Vectorization Opportunities for Improved Performance with Intel® AVX-512 Examples of How Intel® Compilers Can Vectorize and Speed up Loops                                           | 47 |

| Intel® Advisor Roofline Analysis A New Way to Visualize Performance Optimization Trade-Offs                                                                                          | 56 |

| Intel-Powered Deep Learning Frameworks Your Path to Deeper Insights                                                                                                                  | 74 |

## THE CHANGING HPC LANDSCAPE STILL LOOKS THE SAME

Henry A. Gabb, *Principal Engineer* at Intel Corporation, is a long-time high-performance and parallel computing practitioner and has published numerous articles on parallel programming. He was editor/coauthor of "Developing Multithreaded Applications: A Platform Consistent Approach" and was program manager of the Intel/Microsoft Universal Parallel Computing Research Centers.

## Celebrating 20 Years of OpenMP\*

The OpenMP\* application programming interface turns 20 this year. To celebrate, we tapped Michael Klemm (the current CEO of the OpenMP Architecture Review Board, or ARB) and some of his colleagues to give an overview of the newest features in the specification—particularly, enhancements to task-based parallelism and offloading computations to specialized accelerators.

Our feature article covers "The Present and Future of the OpenMP API Specification," so I'll say a little about its past. I half-jokingly refer to the early to mid-1990s as the "bad old days" of high-performance computing (HPC). There were many, many different parallel programming models and parallel architectures dotting a fast-changing HPC landscape. For distributed-memory architectures, there were low-level, message-passing methods like SHMEM, high-level, methods like PVM or MPI, and even higher levels of abstraction with High Performance Fortran and Unified Parallel C. For shared-memory architectures, there were low-level threading methods like Pthreads or higher-level compiler-directed threading. One thing was clear: There were no magic compilers that could automatically parallelize real applications. Parallel compiler directives were the next best thing.

For those of us who remember parallel compiler directives before OpenMP, there were many vendor-specific sets to choose from (e.g., Cray, SGI, Intel, Kuck and Associates, Inc.), each doing the same thing but with different syntaxes. In exasperation, several large governmental HPC facilities demanded a unified syntax for parallel compiler directives.

OpenMP was born in 1997. Most of the original vendors are still on the ARB, and many more members have been added since (the ARB currently has 29 members). It remains the gold standard for portable, vendor-neutral parallel programming directives because it never lost sight of its original purpose.

Today, MPI and OpenMP cover most application requirements in HPC. There are still challenges. Memory subsystems are as unbalanced as ever, different processor architectures now commonly exist within the same system, and keeping data coherent among these different processing elements is an additional burden on the programmer. But MPI and OpenMP continue to evolve with these challenges, so the HPC future looks bright.

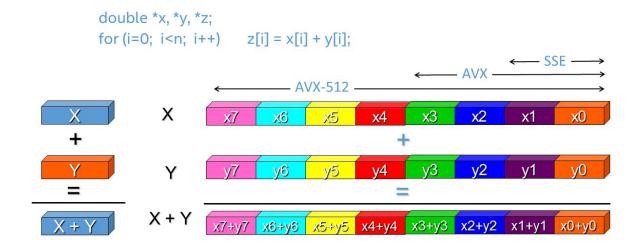

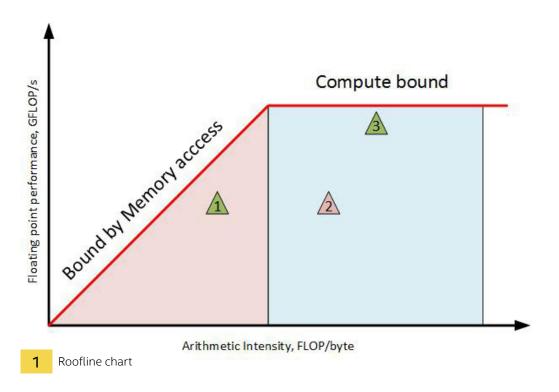

#### **New Tools for Tuning Serial Performance**

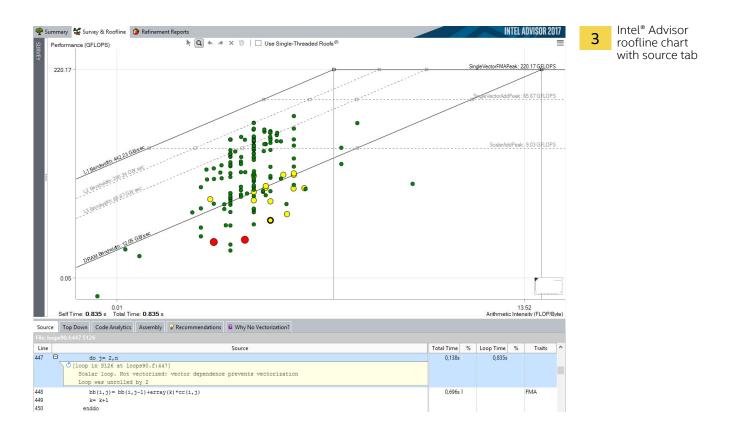

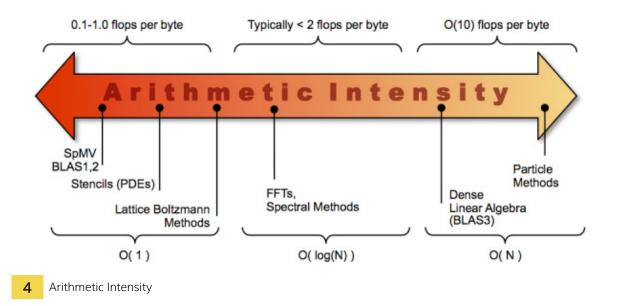

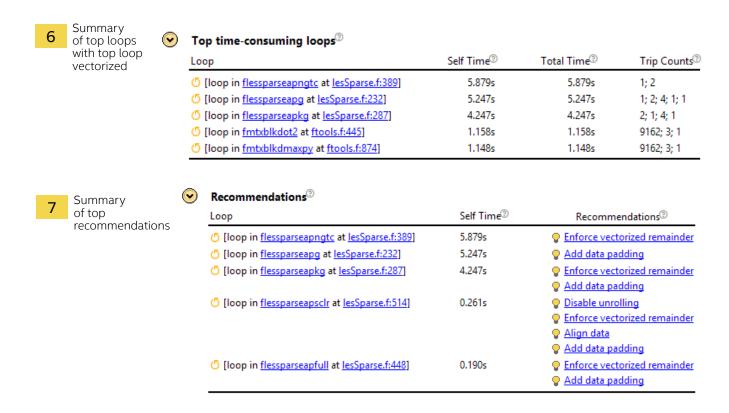

Parallelism is great, but would you parallelize code that has not been properly tuned? No, you wouldn't. So this issue of *The Parallel Universe* also looks at tuning serial performance. My first supercomputer was a Cray X-MP, so I learned early the importance of vectorization. "Vectorization Opportunities for Improved Performance with Intel® AVX-512" gives a good overview of tuning code with the new Intel AVX-512 instruction set and shows how to use these instructions to expose vectorization opportunities that were not previously possible. The new Intel® Advisor Roofline and Intel® VTune™ Amplifier Memory Analysis features help visualize performance optimization tradeoffs and how memory access is affecting an application's performance. These features are demonstrated in "Intel® Advisor Roofline Analysis" and "Identify Scalability Problems in Parallel Applications." We round out this issue with tips for optimizing general matrix-matrix multiplication operations in the Intel® Math Kernel Library ("Reducing Packing Overhead in Matrix-Matrix Multiplication") and a brief overview of Intel software support for machine learning ("Intel-Powered Deep Learning Frameworks").

#### Hello, I'm New Here

Finally, I'd like to introduce myself as the new editor of *The Parallel Universe*. I've been doing HPC since about 1990, but I was originally doing research in computational life science. Each successive research project required more computing power. To stay relevant, I had to learn about **performance tuning** and parallel programming. My academic background is in biochemistry and genetics, so I resented the intrusion of computer science into my scientific domain. But my initial resistance gave way to fascination when I saw how HPC could change my research and make it possible to answer new and bigger research questions. Hardware and software advances allow me to quickly run simulations on my laptop that once took days on a circa 1995 supercomputer. I used to dread the heterogeneous parallel computing future. Now, I welcome it with the same fascination I had as a young graduate student.

**Henry A. Gabb** January 2017

# THE PRESENT AND FUTURE OF THE OPENMP\* API SPECIFICATION

How the Gold Standard Parallel Programming Language Has Improved with Each New Version

Michael Klemm, Senior Staff Application Engineer, Intel Deutschland GmbH; Alejandro Duran, Application Engineer, Intel Corporation Iberia; Ravi Narayanaswamy, Senior Staff Development Engineer; Xinmin Tian, Senior Principal Engineer; and Terry Wilmarth, Senior Development Engineer, Intel Corporation

There are two decades of history associated with the OpenMP\* API and, since its inauguration, OpenMP features have been added to keep up with developments in hardware and software to ensure that you can use it to program the hardware that you have. Since the release of version 4.0 in 2013, the OpenMP language has supported heterogeneous and SIMD programming. Similarly, support for programs with irregular parallelism was improved in 2008 with the addition of tasking constructs. OpenMP Technical Report 4: Version 5.0 Preview 1 (TR4 for short) is the next step in the evolution of the OpenMP language. It adds task reductions, extends SIMD parallel programming, and considerably extends the productivity of heterogeneous programming. In this article, we review existing OpenMP features and provide a preview of what will be coming soon in implementations supporting TR4.

## Tasking: Express Yourself with Tasks

Tasking, or task-based programming, is an important concept for applications that require irregular parallelism (e.g., recursive algorithms, graph traversals, and algorithms operating on unstructured data). Since OpenMP version 3.0, the task construct has provided a convenient way to express the concurrent execution of small units of work that are handed to a scheduler in the OpenMP runtime system.

```

void taskloop_example() {

#pragma omp taskgroup

{

#pragma omp task

long_running_task() // can execute concurrently

#pragma omp taskloop collapse(2) grainsize(500) nogroup

for (int i = 0; i < N; i++)

for (int j = 0; j < M; j++)

loop_body();</pre>

```

1 Simple example using the new taskloop construct together with an OpenMP\* task

**Figure 1** illustrates the creation of an OpenMP task to execute a long-running function and then a loop that has been parallelized using the <code>taskloop</code> construct. This construct appeared with OpenMP 4.5 and provides syntactic sugar to allow programmers to easily parallelize loops using OpenMP tasks. It divides the loop iteration space into chunks and creates one task for each chunk. The construct supports several clauses to allow fine control (e.g., <code>grainsize</code> to control the amount of work per task and <code>collapse</code> to create a product loop out of the <code>i</code> and <code>j</code> loops). TR4 extends the expressiveness of OpenMP tasks by defining new clauses for the <code>taskgroup</code>, <code>task</code>, and <code>taskloop</code> constructs to perform reductions across the generated tasks.

**Figure 2** illustrates the creation of tasks to process a linked list and find the minimum value of all elements in the list. The **parallel** construct creates a parallel region to have worker threads available for task execution. The **single** construct then restricts execution to one thread that traverses the linked list and generates one task for each list item via **omp** task. This is a common way to implement a producer-consumer pattern in OpenMP.

Task reductions in TR4 use the taskgroup construct that was introduced in OpenMP version 4.0. It was designed to group tasks logically and to provide a way to await completion of all the tasks in the group. TR4 extends the taskgroup construct to perform reductions through the task\_reduction clause, as illustrated in Figure 2. If this clause is added to the construct, all partial results gathered by the individual tasks are aggregated to form the final result at the end of the taskgroup region. Tasks that contribute to the reduction operation must have an in\_reduction clause that matches the reduction clause of their taskgroup.

Starting with TR4, the taskloop construct supports the reduction and in reduction clauses with their task reduction semantics. If a reduction clause appears on the taskloop construct, an implicit task group is created, which performs the requested reduction operation at the end of the loop. If an in reduction clause is added, the tasks generated by the taskloop construct participate in the reduction of an outer taskgroup region.

```

int find_minimum(list_t * list) {

int minimum = INT MAX;

list_t * ptr = list;

#pragma omp parallel

#pragma omp single

#pragma omp taskgroup task_reduction(min:minimum)

for (ptr = list; ptr ; ptr = ptr->next) {

#pragma omp task firstprivate(ptr) in_reduction(min:minimum)

int element = ptr->element;

minimum = (element < minimum) ? element : minimum;</pre>

}

}

return minimum;

```

Traversing a linked list and computing the minimum using task reductions

## Offloading: Making the Most of Coprocessors

The OpenMP API strives to improve the usability of offloading pragmas based on user feedback. To that end, new features have been added to TR4 and some existing features have been enhanced. One of the key new features is the ability to automatically detect functions used in offload regions and treat them as if they appeared in a declare target directive. Previously, all functions called in an offload region had to be explicitly tagged using declare target directives. This was hard work, especially if the routines were in header files not owned by the programmer (e.g., the Standard Template Library), and would require declare target directives on the header file itself, which would create a copy of every function in the header file for the device even if some functions were not used in the offload region.

```

#pragma omp declare target

void foo() {

// ...

}

#pragma omp end declare target

void bar() {

#pragma omp target

{

foo();

}

}

void foo() {

// ...

}

// ...

}

**The pragma omp end declare target

void bar() {

#pragma omp target

{

foo();

}

}

**The pragma omp target

{

foo();

}

}

```

3 Automatically detect functions used in offload regions

In **Figure 3**, the code on the left shows what was required in OpenMP version 4.5. Starting with TR4, the code on the right side is sufficient due to the implicit detection and creation of the device function.

Automatic detection also extends to variables with static storage duration in TR4. The examples in **Figure 4** are equivalent.

```

int x;

#pragma omp declare target to (x)

void bar() {

#pragma omp target

{

x = 5;

}

}

void bar() {

#pragma omp target

{

x = 5;

}

}

```

4 Automatic detection for variables with static storage duration

OpenMP version 4.5 introduced the use\_device\_ptr clause. The variable in use\_device\_ptr must be mapped before it can be used. To achieve this, the programmer would need to use a separate #pragma target data clause, as a variable can appear in only one data clause. Thus, the OpenMP directives in **Figure 5** are needed.

```

#pragma omp target data map(buf)

#pragma omp target data use_device_ptr(buf)

```

Mapping the variable

In TR4, an exception has been made so that the variable can appear in both the map and use device ptr clauses in a single construct, as shown in Figure 6.

```

#pragma omp target data map(buf) use device ptr(buf)

```

Variable can appear in both the map and use device ptr clauses

Static data members are now permitted in a class inside an omp declare target construct. Class objects with static members can also be used in a map clause (Figure 7).

```

#pragma omp declare target

class C {

static int x;

int y;

class C myclass;

#pragma omp end declare target

void bar() {

#pragma omp target map(myclass)

mvclass.x = 10

}

```

Class objects with static members used in a map clause

In addition, virtual member functions are allowed in classes inside an omp declare target construct or objects used in a map clause. The only caveat is that the virtual member functions can be invoked only on a device if the object is created on the same device.

In OpenMP 4.5, scalar variables used in a reduction or lastprivate clause on a combined construct for which the first construct is target are treated as firstprivate for the target construct. That results in the host value never being updated, surprisingly. To update the value on the host, the programmer had to separate the omp target directive from the combined construct and explicitly map the scalar variable. In TR4, such variables are automatically treated as if they had a map (tofrom: variable) applied to them.

If a section of a named array is mapped using omp target data, any nested omp target inside the omp target data construct that references the array would require an implicit mapping to either the same section or a subsection of the array used in the outer omp target data map clause. If the explicit mapping is omitted on the inner omp target region, the implicit mapping rule kicks in, which would imply that the entire array is mapped according to OpenMP version 4.5. This would result in a runtime error from mapping a larger-sized array when a subsection of the array is already mapped. Similarly, mapping a field of a structure variable in the outer omp target data construct and using the address of the structure variable inside a nested omp target construct would result in an attempt to map the entire structure variable when part of the structure is already mapped. TR4 has fixed these cases to give the behavior that programmers typically expect (Figure 8).

8 Improved mapping

The new features in TR4 improve the programmability of offloading using OpenMP, requiring fewer modifications to the application. The automatic detection of variables and functions used in <code>target</code> regions removes the need for explicit specification. Similarly, the elimination of the need to repeat <code>map</code> clauses inside nested regions and allowing variables to appear in both <code>map</code> and <code>use\_device\_ptr</code> reduces the number of OpenMP directives required. The changes to the behavior of reduction variables aligns the language with programmer expectations. Overall, the cleaner semantics make the use of offload devices within OpenMP applications simpler and more intuitive.

## **Efficient SIMD Programming**

## SIMD Loops with Cross-Iteration Dependencies

OpenMP version 4.5 extends the ordered construct by adding a new simd clause. The ordered simd construct declares that a structured block in the SIMD loop or SIMD function must be executed in iteration order or in the order of function calls, respectively. Figure 9 shows the use of the ordered simd block to preserve read-write, write-read, and write-write ordering within each iteration and among iterations, while the entire loop can be executed concurrently using SIMD instructions. In the first ordered simd block, the index ind[i] of array a may have a write-write conflict (e.g., ind[0] = 2, ind[2] = 2), so it needs to be serialized by the ordered simd to allow vectorization of the entire loop. In the second ordered simd block, the myLock(L) and myUnlock(L) operations must be in a single ordered simd block. Otherwise, as part of the loop vectorization (e.g., for a vector length of two), the calls to myLock(L) and myLock(L) will be expanded to two calls as follows: {myLock(L); myUnlock(L); myUnlock(L);}. Nesting the lock functions will typically result in a deadlock. The ordered simd construct shown in the example creates the proper sequence {myLock(L); ...; myUnlock(L); ...; myUnlock(L);}.

```

#pragma omp simd

#pragma omp simd

for (i = 0; i < N; i++) {

for (i = 0; i < N; i++) {

#pragma omp ordered simd

#pragma omp ordered simd

// write-write conflict

if (c[i]) > 0) q[j++] = b[i];

a[ind[i]] += b[i];

// ...

#pragma omp ordered simd

// ...

#pragma omp ordered simd

if (c[i] > 0) q[j++] = d[i];

// atomic update

myLock(L)

if (x > 10) x = 0;

}

myUnlock(L)

// ...

}

```

9 Preserving read-write, write-read, and write-write ordering within each iteration and among iterations

When using the simd clause on the ordered construct, caution is required to not violate inherent dependencies between two ordered simd blocks. Figure 9 shows incorrect uses of #pragma omp ordered simd, as the order of stores is changed under SIMD execution with respect to its serial execution. Assume c[0] = true and c[1] = true. When the above loop is executed serially, the order of stores is: q[0] = b[0], q[1] = d[0], q[2] = b[1], q[3] = d[1], and so forth. However, when the loop is executed concurrently with a

vector length of two, the order of stores is: q[0] = b[0], q[1] = b[1], q[2] = d[0], q[3] = d[1], ... The change in store ordering is due to a violation of the write-to-read dependency on the variable j between the two ordered simd blocks in the loop. The correct use is to merge the two ordered simd blocks into a single ordered simd block.

## **REF/UVAL/VAL Modifier Extensions to the Linear Clause**

The linear clause provides a superset of the functionality provided by the private clause. When a linear clause is specified on a construct, the value of the new list item on each iteration of the associated loop(s) corresponds to the value of the original list item before entering the construct, plus the logical number of the iterations multiplied by the linear step. The value corresponding to the sequentially last iteration of the associated loop(s) is assigned to the original list item. When a linear clause is specified on a declarative directive, all list items must be formal parameters (or, in Fortran, dummy arguments) of a function that will be invoked concurrently on each SIMD lane.

The rationale behind adding ref/uval/val modifiers to the linear clause is to provide a way for programmers to precisely specify the linear or uniform property of memory references with respect to address and data value so the compiler can leverage the information to generate efficient SIMD code using unit-stride loads/stores instead of gathers/scatters. Essentially, for implicitly referenced linear arguments, it would be better to have reference as linear. The semantics of uval/val/ref is described as:

- linear(val(var):[step]) indicates that the value is linear even if the var is passed by its reference. The vector of addresses is passed for passed by reference. In this case, the compiler must generate gathers or scatters.

- linear(uval(var):[step]) indicates that the value passed by reference is linear while the reference itself is uniform. So the reference to the first lane is passed, but other values can be constructed using step. The compiler can use general-purpose registers to pass the base address and compute its linear value.

- linear(ref(var):step) indicates that the parameter is passed by reference, the underlying reference is linear, and the memory access will be linear unit-stride or nonstrided depending on step. The compiler can use general-purpose registers to pass the base address and compute its linear address.

**Figure 10** shows a function **FOO** with arguments X and Y, which are pass-by-reference in Fortran. The "**VALUE**" attribute does not change this behavior. It says only that the updated value will not be visible to the caller per the Fortran 2008 language specification. Since the references of X and Y are not annotated as linear, the compiler must generate gather instructions to load (XO, X1, X2, X3) and (YO, Y1, Y2, Y3), assuming the vector length is four. In **Figure 11**, the references to X and Y are annotated as linear, so the compiler can generate unit-stride SIMD loads for much better performance.

10 Linearity of reference X and Y is unknown at compile time

11 References to X and Y annotated as linear

In **Figure 12**, the function add\_one is annotated as a SIMD function. It has a C++ reference argument **const** int &p. Assuming a vector length of four, if p is annotated as linear(ref(p)), the compiler can generate the unit-stride load instruction with the base address p in the rax register to load p[0], p[1], p[2], and p[3] to the xmm0 register. In that case, the add\_one function requires only three instructions.

```

#pragma omp declare simd notinbranch // linear(ref(p))

__declspec(noinline)

int add_one(const int& p) {

return (p + 1);

}

```

12 SIMD code comparison with and without linear(ref(p)) annotation

However, if p is not annotated as linear(ref(p)), the compiler has to assume that four different addresses p0, p1, p2, and p3 are passed in via two xmm registers, and the gather operation is emulated with a sequence of scalar load and packing instructions. As a result, the add one function now requires 16 instructions rather than three.

Overall, the additional SIMD features in OpenMP version 4.5 allow the user to provide more information to the compiler, which allows vectorization of more loops and the generation of better vector code in many circumstances.

## Affinity: Thread Placement Made Easy

The OpenMP version 4.0 specification gave users a standard way to control thread affinity for the first time. It introduced two new concepts to the language:

- 1. Binding policy

- 2. Place partition

The binding policy, specified by the bind-var Internal Control Variable (ICV), determines where the threads of a team will be bound relative to the parent thread's place. The place partition, specified by the place-partition-var ICV, is the set of places to which threads can be bound. Once a thread is bound to a place for a given team, it should not be moved from that place.

There are three binding policies defined by the specification: master, close, and spread. In describing these policies, we will consider a set of four places, each one a core with two threads. We will show examples of placing three threads and six threads on those places, and we assume that the parent thread will always be on the third place. In the master policy, the master thread is bound to the parent thread's place, and then the remaining threads in the team are assigned to the same place as the master thread (**Table 1**).

|               | Place 1: {0,1} | Place 2: {2,3} | Place 3: {4,5} (parent) | Place 4: {6,7} |

|---------------|----------------|----------------|-------------------------|----------------|

| Three threads |                |                | 0, 1, 2                 |                |

| Six threads   |                |                | 0, 1, 2, 3, 4, 5        |                |

**Table 1.** Thread placement for the master policy

The close policy starts by placing the master thread on the parent thread's place, and then proceeds in a round-robin fashion with the remaining threads in the team. To place **T** threads on P places, the master's place gets roughly the first T/P threads, then the next place in the place partition gets the next T/P threads, and so on, wrapping around in the place partition as needed, giving a distribution (**Table 2**).

|               | Place 1: {0,1} | Place 2: {2,3} | Place 3: {4,5} (parent) | Place 4: {6,7} |

|---------------|----------------|----------------|-------------------------|----------------|

| Three threads | 2              |                | 0                       | 1              |

| Six threads   | 4              | 5              | 0,1                     | 2,3            |

**Table 2.** Thread placement for the close policy

With the spread policy, things get very interesting. The placement of threads will be such that they are spread out over the available places. This is accomplished by forming **T** roughly even subpartitions of the place partition, or P partitions if T >= P. If T <= P, each thread gets its own subpartition, starting with the master thread, which will get the subpartition containing the place to which the parent thread is bound. Each subsequent thread is bound to the first place in each subsequent subpartition, wrapping around as needed. If T > P, sets of consecutive threads get the same subpartition, which in this case will consist of a single place. Thus, all the threads in the set will be bound to the same place. We show the subpartitions formed in **Table 3** in curly braces. These are important if nested parallelism is used, since they affect the available resources used by each nested parallel region.

|               | Place 1: {0,1} | Place 2: {2,3} | Place 3: {4,5} (parent)                   | Place 4: {6,7} |  |  |

|---------------|----------------|----------------|-------------------------------------------|----------------|--|--|

| Three threads | 1 {{0,1}}      | 2 {{2,3}}      | 0 {{4,5},{6,7}} Note: 0 is bound to {4,5} |                |  |  |

| Six threads   | 4 {{0,1}}      | 5 {{2,3}}      | 0,1 {{4,5}}                               | 2,3 {{6,7}}    |  |  |

Table 3. Thread placement and subpartitions for the spread policy

OpenMP version 4.0 also provides a query function for the thread affinity binding policy: omp proc bind t omp get proc bind(). It returns the binding policy to be used in the next parallel region (assuming that no proc bind clause is specified on that region).

What is really interesting about the **spread** policy is what happens with the subpartition. With the master and close policies, each implicit task inherits the place partition of the parent implicit task. But, in the spread policy, implicit tasks get their place-partition-var ICV set to the subpartition instead. This means that a nested parallel construct will have all of its threads placed within the subpartition of its parent.

The value of bind-var can be initialized via the environment variable OMP PROC BIND. The value of bind-var can also be overridden by the addition of a proc bind clause to a parallel construct. Specifying the place-partition-var is accomplished via the OMP PLACES environment variable. Places can be hardware threads, cores, sockets, or specific quantities of those. They can also be explicit processor lists. More details can be found in the OpenMP API specification.

The OpenMP 4.5 specification enhanced the language's affinity capabilities by providing a set of functions capable of querying aspects of the place partition and binding place of the current thread. These new API functions are useful for confirming the correctness of the settings to achieve the programmer's desired thread affinity. This is particularly important when the complexity of the code is high and nested parallelism is used in conjunction with the spread binding policy to place threads in nested parallel regions such that they share lower-level caches. These API functions are:

- int omp get num places(): Returns the number of places in the place-partition-var in the execution environment of the initial task.

- int omp get place num procs(int place num): Returns the number of processors available to the execution environment in the place specified by place num in the place partition.

- void omp\_get\_place\_proc\_ids(int place\_num, int \*ids): Gets the processors available to the execution environment in the place specified by place num in the place partition, allocates an array to hold them, and puts that array at ids.

- int omp get place num(void): Returns the number of the place in the place partition to which the encountering thread is bound.

- int omp get partition num places (void): Returns the number of places in the place partition of the innermost implicit task. Note that this differs from omp get num places() in that it will show the effects of the spread binding policy as the place partition gets broken into subpartitions, whereas omp get num places() will always show the full original place partition.

- void omp get partition place nums(int \*place nums): Gets the list of place numbers corresponding to the place partition of the innermost implicit task and allocates an array in place nums to store them. Note that the place numbers are the numbers of the places in the full original place partition. This function is particularly useful to see which places from the original place partition appear in a subpartition resulting from the use of the spread binding policy.

## CODE CAN SAVE LIVES

## Your code can inspire medical breakthroughs for improved healthcare

Do more with Intel® Parallel Studio XE. It's designed to optimize your parallel code, so you can fast-track your high-performance computing needs to find the right solutions—and diagnosis—quicker.

Code amazing things >

## Outlook on the OpenMP API Specification, Version 5.0

The OpenMP Architecture Review Board (ARB) is discussing other features that could appear in version 5.0 of the OpenMP specification. The most likely candidates are described in this section.

### **Memory Management Support**

How to support increasingly complex memory hierarchies within OpenMP applications is an area of active discussion. This complexity comes from multiple directions: new memories with different characteristics (such as MCDRAM on Intel® Xeon Phi™ Processors or Intel® 3D XPoint™ memory), the need to request certain characteristics of the allocated memory to ensure good performance (e.g., certain alignments or page sizes), the need for special compiler support for some memories, NUMA effects, etc. Furthermore, many new memory technologies are being investigated, so any proposal needs to be extensible to handle future technologies.

The current working direction is based on two key concepts that try to model the different technologies and operations: memory spaces and allocators. Memory spaces represent system memory with a set of traits (e.g., page size, capacity, bandwidth, etc.) that programmers can specify to find the memory that they want their program to use. Allocators are objects that allocate memory from a memory space and can also have traits that alter their behavior (e.g., the alignment of allocations).

New APIs are defined to manipulate memory spaces and allocators, and to allocate and deallocate memory. Separating the calls for creating an allocator and allocating memory allows the construction of maintainable interfaces where decisions about where memory should be allocated are taken in a common "decision" module. **Figure 13** shows how the proposal can be used to select the memory with the highest bandwidth in the system that uses 2 MB pages and defines two different allocators from that memory: one that ensures allocations are 64-byte-aligned and one that does not.

13 Selecting the memory with the highest bandwidth

A new allocate directive is proposed to affect the underlying allocation of variables that are not allocated with an API call (e.g., automatic or static variables). A new allocate clause can be used to affect the allocations done by OpenMP directives (e.g., private copies of variables). **Figure 14** shows how to use the directive to change the allocation of variables a and b to a memory with the highest bandwidth that also uses 2 MB pages. The private copies of b in the parallel region of the example are allocated on a memory with the lowest latency.

14 Changing the allocation of variables a and b to a memory with the highest bandwidth that also uses 2 MB pages

### Improvements for Heterogeneous Programming

Several features are being considered to improve OpenMP's device support:

- Currently, structures in a map clause are bitwise copied, including pointer fields in a structure. If the programmer requires the pointer field to point to valid device memory, that would require creating the device memory and explicitly updating the pointer field on the device. The committee is discussing extensions that would enable the programmer to specify the automatic attaching/detaching of the pointer fields in a structure using a map clause by extending it to support pointer fields in structures.

- The ARB is considering allowing function pointers to be used in a target region and also allowing a function pointer to appear in declare target.

- New device memcpy routines that can execute asynchronously.

- Support to enable an "execute on device or fail" semantics of the target construct. Currently, target regions can execute silently on the host when the device is not available.

- Support for variables and functions that only exist on devices and are not copies of host-based ones.

- Support for multiple types of devices in a single application.

## **Tasking Improvements**

Beyond the features discussed in this article, other features being considered for OpenMP 5.0 are:

- Enabling data dependencies between taskloop constructs.

- Enabling data dependencies in both the task construct and taskloop construct to contain expressions that could be expanded to multiple values to generate more than dependence from a single depend clause.

- Providing support to express task to thread affinity with patterns similar to those of OMP PROC BIND.

## **Other Changes**

Other areas where there are active discussions of additional features for OpenMP 5.0 include:

- Upgrade the OpenMP base language specification to C11, C++11, or C++14, and Fortran 2008.

- Relax the restrictions of the collapse clause to allow nonrectangular loop shapes and allow code to appear between the loops in the nest.

- Allow reductions to happen in the middle of a parallel region without being associated with a work-sharing construct.

The OpenMP API is the gold standard of a portable and vendor-neutral parallel programming language for shared memory parallelization of C, C++, and Fortran applications in highperformance computing and beyond. And with upcoming developments in version 5.0, it promises to offer much more for developers to fully utilize the capabilities of modern processors.

## **BLOG HIGHLIGHTS**

## Code Modernization: Powering Scientific Discovery and Fostering Innovation Globally at CERN (Part 2)

BY RUSS BEUTLER (INTEL) >

Intel recently talked to CERN openlab CTO Maria Girone to discuss how CERN and Intel work together to deliver improvements in processing speed, sometimes by factors, and how that impacts CERN's research on the basic constituents of matter. This conversation is meant to help developers understand how a Modern Code approach can help advance research and breakthroughs globally.

In Part 2 of the interview, Maria offers advice for developers around building a code modernization strategy and discusses the programs available to enable developers and students to develop their skills, advance their careers, and bring large-factor improvements to the applications they work with.

What advice do you have for developers and companies building a code modernization strategy and looking to ensure that their applications take full advantage of modern server hardware?

First, it's important to recognize that there's room for significant improvement when it comes to legacy code. And that it represents a good career opportunity for developers who are good at updating it.

Then, specifically, they should work to understand the gap between where their legacy software currently stands performance-wise, and the gains achievable through efficient parallelization and vectorization. Next, it's important to demonstrate the improvements that can be made by undertaking a code modernization effort.

**Read more**

## REDUCING PACKING OVERHEAD IN MATRIX-MATRIX MULTIPLICATION

Improve Performance on Multicore and Many-Core Intel® Architectures, **Particularly for Deep Neural Networks**

Kazushige Goto, Murat Efe Guney, and Sarah Knepper, Software Development Engineers, Intel Corporation

General matrix-matrix multiplication (GEMM) is a fundamental operation in many scientific, engineering, and machine learning applications and is one of the key routines in the BLAS (basic linear algebra subprograms) domain. Four precisions (real single, real double, complex single, and complex double) of GEMM exist. In this article, we focus on SGEMM (real single precision).

The Fortran API for SGEMM is:

It performs the computation:

SGEMM(transa, transb, m, n, k, alpha, A, lda, B, ldb, beta, C, ldc)

$C := alpha * op(A) * op(B) + beta * op(C), where op(X) = X or X^T$ (depending on the value of the transx parameter).

The arrays A and B are inputs, while C is both input and output. Array A contains an m-by-k matrix, array B a k-by-n matrix, and array C an m-by-n matrix. The leading dimensions (lda, ldb, and ldc) determine the stride from one column to the next, allowing GEMM to work on portions of a larger matrix. Leading dimensions can also impact the performance by causing subsequent columns to be cache line-aligned or to map to the same set on the 8-way level-1 cache.

Intel® Math Kernel Library (Intel® MKL) offers high-performing GEMM implementations. The typical approach for optimizing matrix-matrix multiplication is to transform blocks of the original input matrices into an internal data format (such as a packed format), multiply transformed blocks via a handwritten assembly kernel, and then update the output matrix.¹ Block sizes are chosen to maximize cache and register usage. The reasons to pack are numerous:

- The ability to fit more data from A and B into the caches, which allows for bigger blocking and more data reuse

- Contiguous, aligned, and predictable accesses, which minimize cache and data translation lookaside buffer (DTLB) misses

- A reduction in loop overhead

For conventional sizes in high-performance computing, this packing-based approach works well. In general here, m and n are relatively large, while k may be moderate (outer product) or also relatively large (square), so that the amount of time spent packing the input matrices is small, relative to the time spent in the computational kernel. However, for sizes where one of m or n is relatively small, as is common for some machine learning applications, the packing overhead can become significant. As a result, a GEMM implementation that does not rely on explicit packing can outperform a conventional, packing-based GEMM implementation. Intel MKL 11.3 Update 3 includes {S,D}GEMM kernels that are optimized for some of these skewed sizes for Intel® Advanced Vector Extensions 2 (Intel® AVX2) and Intel® Advanced Vector Extensions 512 (Intel® AVX-512) and on the 2nd generation of the Intel® Xeon Phi™ processor. Later versions of Intel MKL continue to improve these kernels.

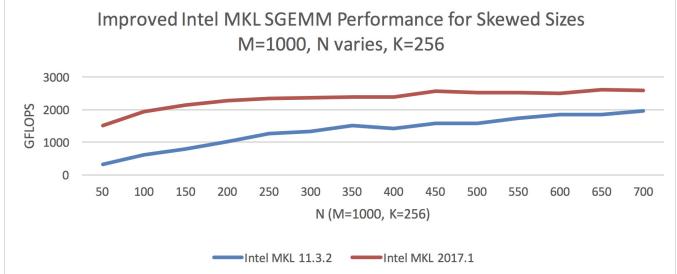

To see an example of the benefit these new kernels can provide, **Figure 1** compares the performance of SGEMM in Intel MKL 2017 Update 1 with that of Intel MKL 11.3 Update 2 for sizes that may arise in machine learning. Here,  $\mathbf{m}$  and  $\mathbf{k}$  are fixed to 1000 and 256, respectively, while  $\mathbf{n}$  varies. The performance is given in gigaflops (billions of floating-point operations per second), so higher is better.

Configuration Info – Versions: Intel® Math Kernel Library (Intel® MKL) 11.3.2 and Intel® MKL 2017.1; hardware: Intel® Xeon® processor E5-2699v4, two 22-core CPUs (55 MB LLC, 2.2 GHz), 64 GB of RAM; operating system: RHEL 7.2 GA x86\_64.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. \*Other names and brands may be claimed as the property of others. Benchmark Source: Intel Corporation

Optimization Notice: Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice. Notice revision #20110804.

1 Improved Intel® MKL SGEMM performance for skewed sizes

Based on the particulars of the SGEMM call (including processor type and thread count, problem size and leading dimensions, and transposition parameters), Intel MKL chooses to use either the conventional kernels or the new packing-free kernels. Deep learning frameworks that rely on Intel MKL for SGEMM performance benefit from these optimizations without requiring modification to the frameworks.

Another way to minimize the packing overhead arises when one or more of the input matrices (A or B) is reused in multiple matrix multiplications; for example, this can arise during recurrent neural networks. Here, we can pay the cost to pack the reused matrix once and then use the packed version in multiple SGEMM computations. Intel MKL 2017 introduced packed APIs for {S,D}GEMM that allow the packing overhead to be amortized over multiple matrix multiplications. For single precision, the four new packed APIs are:

```

dest = sgemm_alloc (identifier, m, n, k)

sgemm_pack (identifier, trans, m, n, k, alpha, src, ld, dest)

sgemm_compute (transa, transb, m, n, k, A, lda, B, ldb, beta, C, ldc)

sgemm_free (dest)

```

The parameters are similar to those of SGEMM, with the addition of the identifier character, which identifies which matrix (A or B) is to be packed. The transa and transb parameters of sgemm compute can be set to "T" (transpose) or "N" (no transpose) as usual; additionally, a value of P indicates that the corresponding matrix is in the internal packed format. The packed APIs provide benefit if an input matrix is used multiple times; thus, sgemm alloc and sgemm pack would each be called once to allocate memory and pack the desired matrix in the internal packed format, respectively, followed by multiple calls to sgemm compute where the packed matrix is passed as one of the input matrices. Finally, **sgemm** free is called to release the memory. (For further details, please see the Intel® Math Kernel Library Developer Reference.)

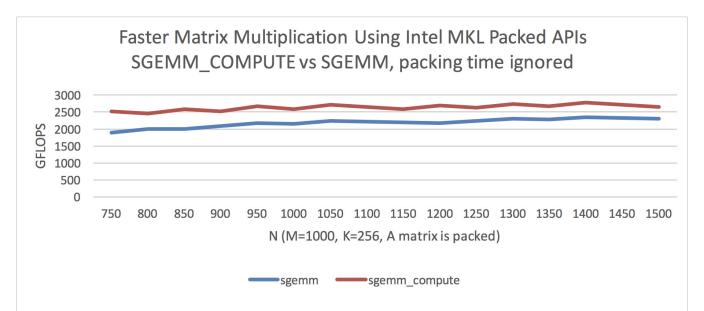

Figure 2 shows a comparison of the performance of sgemm and sgemm compute (where the A matrix is packed and the packing time is ignored) in gigaflops.

Configuration Info - Versions: Intel® Math Kernel Library (Intel® MKL) 2017.1; Hardware: Intel® Xeon® Processor E5-2699v4, 2 22-core CPUs (55MB LLC, 2.2GHz), 64GB of RAM; Operating System: RHEL 7.2 GA x86 64

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. \*Other names and brands may be claimed as the property of others. Benchmark Source: Intel Corporation

Optimization Notice: Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice. Notice revision #20110804

Faster matrix multiplication using Intel® MKL packed APIs

Applications that reuse the larger of the A and B input matrices between GEMM calls have the greatest potential to benefit from packed APIs. If both  $\mathbf{m}$  and  $\mathbf{n}$  parameters are large, or if the smaller of the two input matrices is reused, the performance improvements from switching to packed APIs may not be significant enough to justify the programming effort. Therefore, we recommend measuring the performance of the particular use case before modifying the application code to employ packed APIs.

As we have seen, the internal packing operation as found in a conventional GEMM implementation can have a noticeable overhead, particularly for sizes with one or more small dimensions. This overhead can be reduced by using kernels that avoid explicitly packing the input matrices or by amortizing the cost of packing over multiple GEMM computations. Starting from Intel MKL 11.3 Update 3, {S,D}GEMM can choose to use kernels that operate directly on the input matrices without first packing to internal buffers; which kernels are used is determined at runtime based on problem characteristics and processor information. Alternatively, Intel MKL 2017 introduced packed APIs that allow one or both of the input matrices to be explicitly packed and then reused in multiple matrix-matrix computations. These two approaches help to achieve high GEMM performance on multicore and many-core Intel® architectures, particularly for sizes arising from deep neural networks.

1. Kazushige Goto and Robert A. van de Geijn. 2008. "Anatomy of High-Performance Matrix Multiplication." ACM Transactions on Mathematical Software, 34, 3, Article 12, May 2008.

## TRY INTEL® MATH KERNEL LIBRARY (INTEL® MKL) TODAY >

# IDENTIFY SCALABILITY PROBLEMS IN PARALLEL APPLICATIONS

How to Improve Scalability for Intel® Xeon and Xeon Phi™ Processors Using New Intel® VTune™ Amplifier Memory Analysis

Vladimir Tsymbal, Software Technical Consulting Engineer, Intel Corporation

With the constantly increasing number of computing cores in modern systems, we expect wellparallelized software to increase performance—preferably linearly—with the number of cores. However, there are some factors limiting parallelism and scalability on multicore systems. We are not going to cover all of them in this article. But in most cases, the limitation is due to the implementation of parallelism:

- Load imbalance that leads to idle threads and CPU cores.

- Excessive synchronization and, as a result, wasted CPU time in spin-waiting and other nonproductive work.

- Parallel runtime library overhead, which might be due to misuse of the library API.

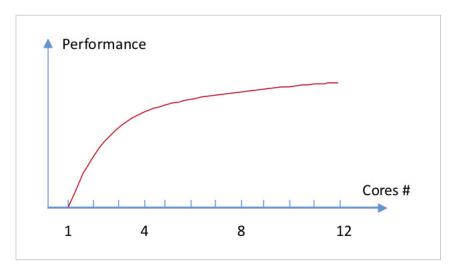

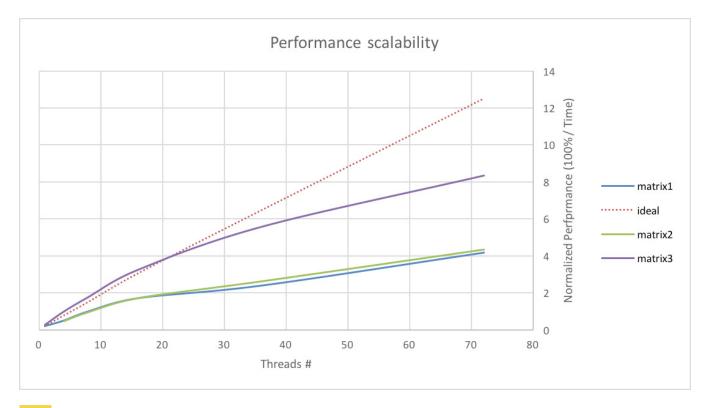

When those limiting factors are eliminated, parallel efficiency improves significantly—with all CPU cores busy doing useful work. Near-linear speedup is observed on well-tuned benchmarks like STREAM or LINPACK. However, with the increasing number of cores on your system (or as you run your code on a newer system with more cores), you might notice that the performance of your application is not increasing linearly—or that parallelism begins to plateau (**Figure 1**).

1 Performance changes according to the number of cores

According to the top-down performance analysis approach,<sup>1</sup> you should first check if other components are limiting performance. Make sure that:

- Your system is not constantly busy with something else that might consume resources, such as other applications or services consuming compute time.

- Your application is not bound to system I/O (e.g., waiting for disk or other file system or network system operations to complete).

- Your system has enough physical memory to avoid frequent swapping to the hard disk drive.

As a common recommendation, you are expected to be aware if your hardware is configured properly and the memory subsystem provides expected performance characteristics. For example, you have all memory slots filled with DIMMs that correspond to the motherboard characteristics (e.g., number of channels, memory speed). You can easily check performance of your hardware with known benchmarks. It's important to do such a check, since it's easier to fix the problem with hardware than with software optimizations.

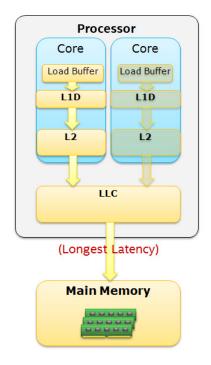

Once all these checks are done, look at memory latency as one of the main reasons for poor parallel scaling. In the x86 systems architecture, the CPU retrieves data from its cache subsystem. Ideally, data resides in the cache closest to the CPU (the L1 data cache) by the time it is needed by instructions (Figure 2). The farther requested data is from the CPU, the longer it takes to travel to the CPU core execution units. A CPU hardware prefetcher should help to bring data in faster, but it's not always possible. Often, data is delayed, which can stall the CPU.<sup>2</sup>

L1D - Data Cache level 1 L2 - Unified Cache level 2 LLC - Last Level Cache Main Memory - DRAM or NVRAM

Retrieving data from the memory subsystem

Basically, there are two reasons why data is late:

- 1. When data is requested by an instruction being executed in an EXE unit of the CPU, data bits make the long trip from the main memory or other caches to the CPU's L1D (i.e., the prefetcher didn't work). This creates a memory latency problem.

- 2. Data is requested in advance (i.e., the prefetcher did its work), but the bits got stuck in traffic on the way to the CPU because of the transport infrastructure capacity. This creates a memory bandwidth problem.

Of course, there might be a combination of both problems if several requests are made from several sources. To avoid these problems, it's important to make smart usage of data. To solve the memory latency problem, ensure that data is accessed incrementally by its address. Sequential data access (or even unit stride, with a constant small distance) makes the prefetcher's life easier—and data access faster. To solve the memory bandwidth problem, reuse data and keep it hot in cache as much as possible. Either solution requires reconsidering data access patterns or even the whole algorithm implementation.

## What's Limiting the Scalability of Your Application?

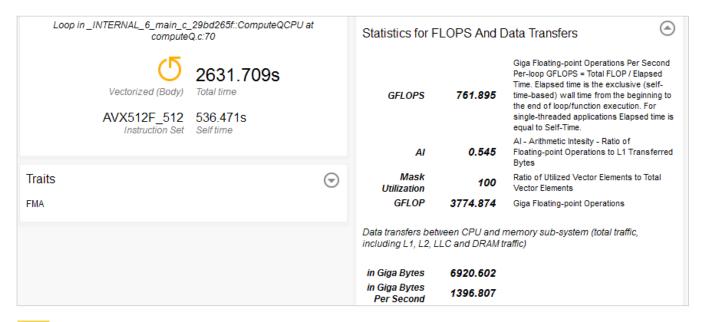

Once we have identified that our code execution is inefficient on a CPU, and we have observed that most stalls are memory bound, we need to define the specific memory problem because the solution is different depending on whether the problem is due to memory latency or bandwidth. We will use Intel® VTune™ Amplifier's embedded memory access analysis for a detailed investigation of memory problems.

Let's consider several iterations of improving a simplified matrix multiplication benchmark. In spite of its simplicity, it effectively demonstrates the possible memory problems that can occur depending on how the algorithm is implemented. For measurements, we will be using an Intel® Xeon® processor E5-2697 v4 (code-named Broadwell, 36 cores) system with known theoretical parameters of memory bandwidth = 76.8 GB/s and double-precision (DP) floating point operations per second (FLOPS) = 662 GFLOPS/s.

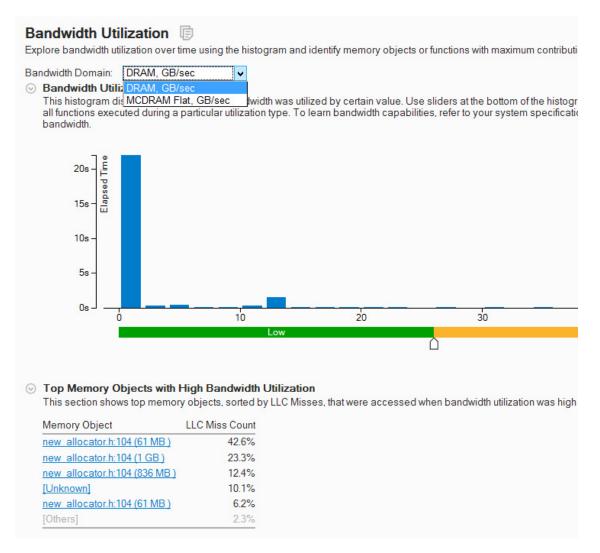

## Naïve Implementation of the Matrix Multiplication Algorithm

The naïve matrix multiplication implementation (multiply1, in **Figure 3**) will never scale linearly to a large number of CPU cores. Nevertheless, for educational purposes, it's a good example to illustrate how to identify causes of inefficient performance. The only improvement we would make is adding the -no-alias compiler option in order to allow **vectorization**. Otherwise, a scalar implementation would be roughly 10 times slower. The results of running the vectorized benchmark multiply1 on matrix size 9216 x 9216 can be found in **Table 1**. Note that the best performance is well below the theoretical maximum FLOPS.

```

void multiply2(int msize, int tidx, int numt, TYPE a[][NUM], TYPE b[][NUM], TYPE c[][NUM], TYPE t[]

[NUM])

int i,j,k;

// Loop interchange

for(i=tidx; i<msize; i=i+numt) {</pre>

for(k=0; k<msize; k++) {</pre>

#pragma ivdep

for(j=0; j<msize; j++) {</pre>

c[i][j] = c[i][j] + a[i][k] * b[k][j];

```

Optimized implementation of the matrix multiplication algorithm (multiply2)

| No. Threads | Elapsed Time, Seconds | DP FLOPS, GFLOPS/Second |

|-------------|-----------------------|-------------------------|

| 4           | 208                   | 7.7                     |

| 8           | 102                   | 15.1                    |

| 16          | 59                    | 26.8                    |

| 36          | 42                    | 37.8                    |

| 72 HT       | 24                    | 66.1                    |

Table 1. Performance and scaling of the naïve matrix multiplication (36 cores, Intel® Xeon® processor E5-2697 v4, two sockets @ 2300 MHz)

As **Table 1** shows, the parallel benchmark is scaling almost linearly with increasing numbers of threads. Scaling begins to plateau when more than 30 cores are involved. The data in **Table 1** might create a false confidence regarding the performance and scaling of the multiply1 benchmark. It's extremely important to understand how much your benchmark is using the compute power of a machine. In our case, the reported FLOPS (determined in the benchmark) is far from the theoretical number calculated for the machine earlier (approximately 10x smaller). The parallel scalability is not limited but the serial performance is. Note that Intel VTune Amplifier indicates the code execution within the loop is inefficient (Figure 4). The low Retiring and high CPI rates help estimate how far we are from practical limits.

|           |                                                                                                                                                  | *      |             | 2     | >>             | >>           | >>            | <b>&gt;&gt;</b> |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------|----------------|--------------|---------------|-----------------|

| S.<br>Li. | Source                                                                                                                                           | Cloc   | Inst<br>Ret |       | Front<br>Bound | Bad<br>Specu | Back<br>Bound | Retiring        |

| 66        | void multiply1(int msize, int tidx, int numt, TYPE a[][NUM]                                                                                      |        |             |       |                |              |               |                 |

| 67        | {                                                                                                                                                |        |             |       |                |              |               |                 |

| 68        | int i,j,k;                                                                                                                                       |        |             |       |                |              |               |                 |

| 69        |                                                                                                                                                  |        |             |       |                |              |               |                 |

| 70        | // Naive implementation                                                                                                                          |        |             |       |                |              |               |                 |

| 71        | for(i=tidx; i <msize; i="i+numt)" td="" {<=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td></msize;>                           |        |             |       |                |              |               |                 |

| 72        | for(j=0; j <msize; j++)="" td="" {<=""><td>38,488</td><td>35,</td><td>1.077</td><td>1.1%</td><td>2.2%</td><td>76.6%</td><td>20.1%</td></msize;>  | 38,488 | 35,         | 1.077 | 1.1%           | 2.2%         | 76.6%         | 20.1%           |

| 73        | for(k=0; k <msize; k++)="" td="" {<=""><td>71,300</td><td>69,</td><td>1.033</td><td>0.0%</td><td>0.0%</td><td>100.0%</td><td>14.7%</td></msize;> | 71,300 | 69,         | 1.033 | 0.0%           | 0.0%         | 100.0%        | 14.7%           |

| 74        | c[i][j] = c[i][j] + a[i][k] * b[k][j];                                                                                                           | 1,867, | 903         | 2.067 | 0.7%           | 0.0%         | 87.1%         | 12.1%           |

| 75        | }                                                                                                                                                |        |             |       |                |              |               |                 |

| 76        | }                                                                                                                                                |        |             |       |                |              |               |                 |

| 77        | }                                                                                                                                                |        |             |       |                |              |               |                 |

| 78        | }                                                                                                                                                |        |             |       |                |              |               |                 |

Performance of the naïve, parallel matrix multiplication benchmark

Next, we'll look at an optimized implementation of the matrix multiplication algorithm (multiply2 in **Figure 3**). If the algorithm is simple enough, and if your compiler is smart enough, it will recognize the inefficient index strides and generate a version with interchanged loops automatically (or you can do that manually).

| No. Threads | Elapsed Time, Seconds | DP FLOPS, GFLOPS/Second |

|-------------|-----------------------|-------------------------|

| 4           | 208.8                 | 7.8                     |

| 8           | 103.3                 | 15.1                    |

| 16          | 58.8                  | 26.4                    |

| 36          | 38.4                  | 40.5                    |

| 72 HT       | 24.7                  | 63.0                    |

Table 2. Performance and scaling of the optimized matrix multiplication (36 cores, Intel® Xeon® processor E5-2697 v4, two sockets @ 2300 MHz)

As you might have noticed from **Table 2**, the absolute numbers are slightly better, but still far from ideal.

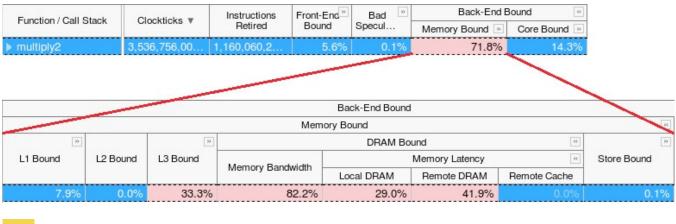

Let's try to understand what's limiting performance and scalability. The General Exploration profiling results (Figure 5) implement yet another top-down analysis approach, this time for CPU microarchitecture.<sup>3</sup> We might notice a couple of interesting things.

**5** General Exploration profiling results

First, notice that the memory latency for bringing data from DRAM to CPU decreased. This is expected, since we implemented contiguous address access in the algorithm. But the memory bandwidth metric is very high. With that in mind, we should check the bandwidth numbers of the main data paths to make sure the DRAM controller and Intel® QuickPath Interconnect (QPI) are not bottlenecks. Second, notice the L3 latency is high as well, even though the data access has a contiguous pattern. This requires additional considerations. High L3 latency meant that we frequently have L2 misses, which is strange because the hardware L2 prefetcher should work (and does work, since the DRAM latency does not decrease with contiguous access). Third, the remote DRAM latency is significant. This indicates that there are nonuniform memory access (NUMA) effects, and some portion of data is fetched from remote DRAM for each node. So, to make the whole picture of data transfers clearer, we need to measure data traffic on the DRAM memory controller and the QPI bus between sockets. For that purpose, we use VTune memory access profiling.

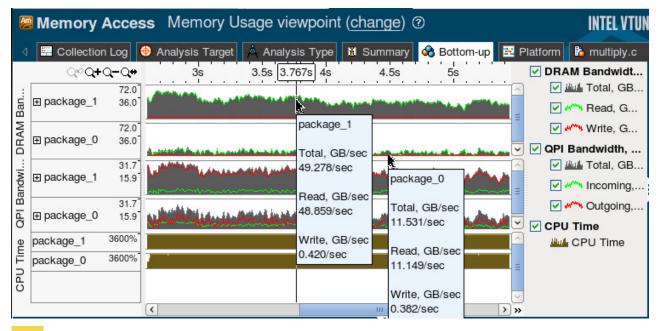

**Figure 6** shows the profiling results for the example with 72 threads. Only one DRAM controller is loaded with data (package\_1), and the average data rate is almost 50 GB/second, which is roughly two-thirds of the maximum bandwidth. On the memory controller of package\_0, the traffic is negligible.

Collecting the Memory Access profile on multiply2 with 72 threads

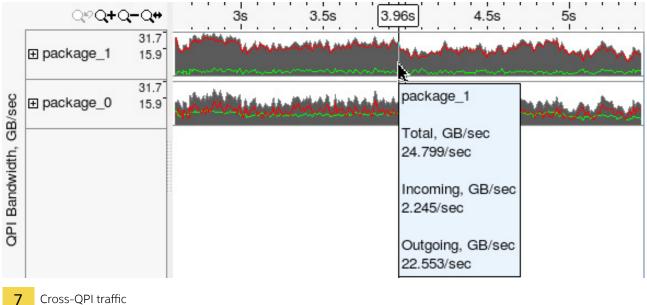

In the same time period, we observe that half of the data traffic in the outgoing QPI lane formed package 1. This explains how the data gets from package 1 DRAM to the package 0 CPU cores (Figure 7). This cross-QPI traffic creates extra latency for data that is being fetched either from remote DRAM by the prefetcher or from remote LLC by a CPU core. Eliminating the NUMA effect might be easy for the benchmark, since the data is well structured and evenly distributed among threads. We just set thread affinities to the CPU cores and have each thread initialize the a, b, and c matrices. But we need to be careful in assuming that allocating data within each thread would eliminate all NUMA effects.

**Figure 8** shows an example that fails to improve performance under the previous assumption, and a way to detect the problem using Intel VTune Amplifier. In the benchmark source code, we introduce a function that represents threads pinned to enumerated CPUs. **Figure 8** shows a part of the code.

```

CreateThreadPool( ... )

{

pthread_t ht[NTHREADS];

pthread_attr_t attr;

cpu_set_t cpus;

pthread_attr_init(&attr);

for (tidx=0; tidx<NTHREADS; tidx++) {

CPU_ZERO(&cpus);

CPU_SET(tidx, &cpus);

pthread_attr_setaffinity_np(&attr, sizeof(cpu_set_t), &cpus);

pthread_create( &ht[tidx], &attr, (void*)start_routine, (void*) &par[tidx]);

}

for (tidx=0; tidx<NTHREADS; tidx++)

pthread_join(ht[tidx], (void **)&status);

}</pre>

```

8 Threads pinned to enumerated CPUs

In a data initialization function, the arrays should be distributed between threads in the same way the arrays are multiplied in the multiplication function. **Figure 9** shows the modification done in the functions to simplify NUMA awareness. In the initialization function, the data array is divided by chunks of size msize/numt, which is the size of the matrix divided by the number of threads. The same is done in the multiplication function shown in **Figure 10**. Surprisingly, the runtime for the benchmark is not much better than the NUMA-unaware version, so let's analyze with an VTune memory access profile (**Figure 11**).

```

InitMatrixArrays (int msize, int tidx, int numt, ...)

{

int i,j,k,ibeg,ibound,istep;

istep = msize / numt;

ibeg = tidx * istep;

ibound = ibeg + istep;

for(i=ibeg; i<ibound; i++) {

for (j=0; j<msize;j++) {

a[i][j] = 1.0*i+2.0*j+3.0;

b[i][j] = 2.0*i+1.0*j+3.0;

c[i][j] = 0.0;

}

}

}</pre>

```

9 Simplifying NUMA awareness

```

multiply2(int msize, int tidx, int numt, ...)

int i,j,k,ibeg,ibound,istep;

istep = msize / numt;

ibeg = tidx * istep;

ibound = ibeg + istep;

for(i=ibeg; i<ibound; i++) {</pre>

for(k=0; k<msize; k++) {

for(j=0; j<msize; j++) {</pre>

c[i][j] = c[i][j] + a[i][k] * b[k][j];

}}}}

```

```

Threads #: 72 Pthreads

Matrix size: 9216

Using multiply kernel: multiply2

Freq = 2.30100 GHz

Execution time = 20.162 seconds

MFLOPS: 72826.877 mflops

```

10 Multiplication function

```

Memory Access Memory Usage viewpoint (change) ③

E Collection Log 🔀 Analysis Target 🛕 Analysis Type 🗓 Summary 🗳 Bottom-up

61.7% of Pipeline Slots

L1 Bound 3:

7.0%

of Clockticks

L2 Bound 12:

14.5% of Clockticks

L3 Bound 3:

26.3% of Clockticks

12.5% of Clockticks

Memory Bandwidth (3):

83.7% of Clockticks

13.1% of Clockticks

Remote / Local DRAM Ratio (2):

1.080

Loads:

244,100,922,808

Stores:

119,604,994,048

352,810,584

Local DRAM Access Count ::

129,603,888

Remote DRAM Access Count 2:

140,004,200

Remote Cache Access Count ::

0

Average Latency (cycles) (2):

55

Total Thread Count:

147

Paused Time (2):

0s

```

11 Memory access profiling

The summary page notifies us that the application is still memory bound (with stalls due to data latencies from memory and data traffic), but the latencies are mostly caused by LLC and less by DRAM. Also, the ratio between local and remote access is very high, which means that the NUMA awareness approach didn't work. If we check the timeline for traffic over the DRAM controller and QPI (**Figure 12**), we see that the data stream from DRAM is hardly reaching 30 percent of peak bandwidth, but the QPI is saturated at approximately 90 percent of its capacity in each direction (the practical limit for QPI is 29.2 GB/s for this system).

12 Checking the timeline for traffic over the DRAM controller and QPI

Remote access (whether DRAM or LLC) is increasing latency for reading memory blocks and making the CPU stall. Those latencies can be measured by Intel VTune Amplifier's memory access, which allows us to identify which data (matrix) is still being accessed in an inefficient, remote way. If we examine the memory analysis summary (**Figure 13**), we can observe which memory objects created most of the latency.

### Top Memory Objects by Latency This section lists memory objects that introduced the highest latency to the overall application execution. Memory Object Stores LLC Miss Count 3 Total Latency Loads mm malloc (648 MB ) 63.5% 112,553,776,512 25,600,384 339,210,176 mm malloc (648 MB) 36.2% 129,952,698,464 118,683,380,224 8,000,240 [Unknown] 5,600,168 0.2% 1,149,634,488 606,409,096 0.0% 120,803,624 201,603,024 0 [Stack] \_mm\_malloc (648 MB ) 0.0% 276,808,304 88,001,320 0 47,201,416 [Others] 0

13 Top memory objects by latency

Among the three top memory objects (represented by their allocation function), we notice that one clearly represents the biggest portion of latencies and is responsible for a large number of load operations (**Figure 14**). Note that only one object has an average latency high enough to conclude that the data is from the remote DRAM of LLC. We can confirm this conclusion by the numbers in the Remote DRAM Access columns.

| Memory Object / Function / Allocation Stack | Loads           | Stores          | LLC Miss Count   |                          |

|---------------------------------------------|-----------------|-----------------|------------------|--------------------------|

|                                             |                 |                 | Local DRAM Acces | Remote DRAM Access Count |

| [Unknown]                                   | 1,149,634,488   | 606,409,096     | 3,200,096        | 3,200,096                |

| _mm_malloc (648 MB )                        | 129,952,698,464 | 118,683,380,224 | 8,800,264        | 0                        |

| _mm_malloc (648 MB )                        | 112,553,776,512 | 25,600,384      | 117,603,528      | 136,804,104              |

| mm_malloc (648 MB )                         | 276,808,304     | 88,001,320      | 0                | 0                        |

14 Memory objects by allocation function

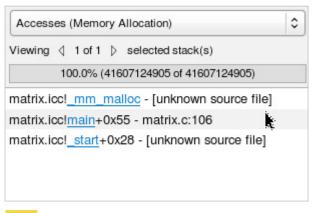

It's easy to figure out that those three objects are the three a, b, and c matrices. The one with high Stores is matrix c. To identify which matrix data is creating high latencies, you need to check the stack for the memory object in the Intel VTune Amplifier stack pane (**Figure 15**). Going by the stack in the user code, we can drill down to the source line of data allocation presented in the Intel VTune Amplifier Source View (**Figure 16**). In this case, it's a matrix b data that creates latency chatter and an increased number of loads. Now we need to understand why it's happening despite the fact that the data arrays were allocated and initialized within pinned threads.

15 Memory objects by stack pane

16 Intel® VTune™ Amplifier source view

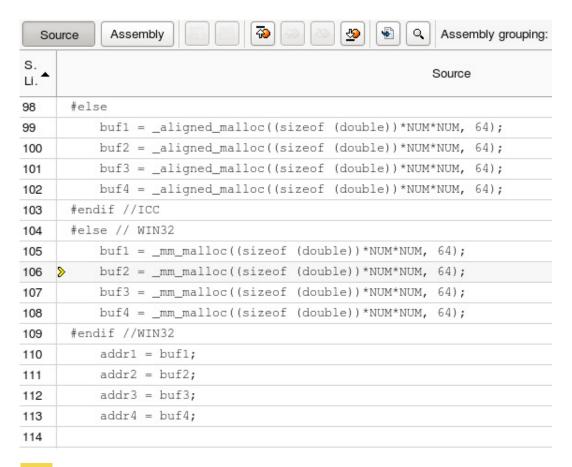

A quick investigation of the algorithm with transposed matrices reveals a fundamental inefficiency in the data access pattern (Figure 17). For each matrix a row, the whole matrix b has to be read entirely from memory.

The matrices include about 9K elements in a column/row. So, the whole matrix memory block size will exceed any CPU cache capacity, generating constant cache data eviction and reloads from DRAM. Even though the distributed rows of matrices **c** and **a** are accessed by threads on the CPU cores on which they were allocated, it doesn't completely apply to matrix **b**. Half of the matrix **b** data will be read by threads from a remote socket in this implementation of the algorithm. Even worse, reading the whole matrix **b** for each row of matrix **a** creates a redundant data load operation (N times more than needed) and generates excessive traffic on QPI for accessing remote data.

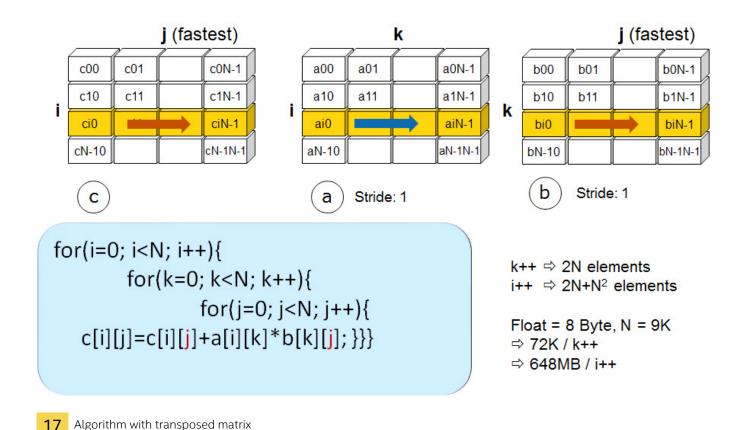

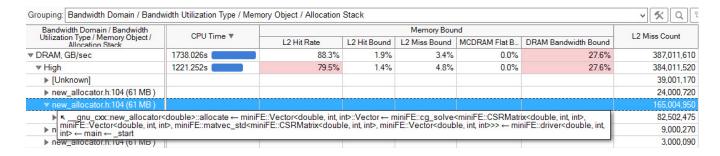

Similarly, you can define which data objects were contributing to increased traffic for DRAM or MCDRAM on Intel Xeon Phi processor-based systems. You just need to select which memory domain traffic you want to analyze. You can get the objects' reference and allocating stack information (**Figure 18**) and, when grouped by bandwidth Domain and bandwidth Utilization Type, you can observe the objects and identify those that contribute most to the L2 Miss Count (**Figure 19**).

Analyzing memory domain traffic

Bandwidth domain

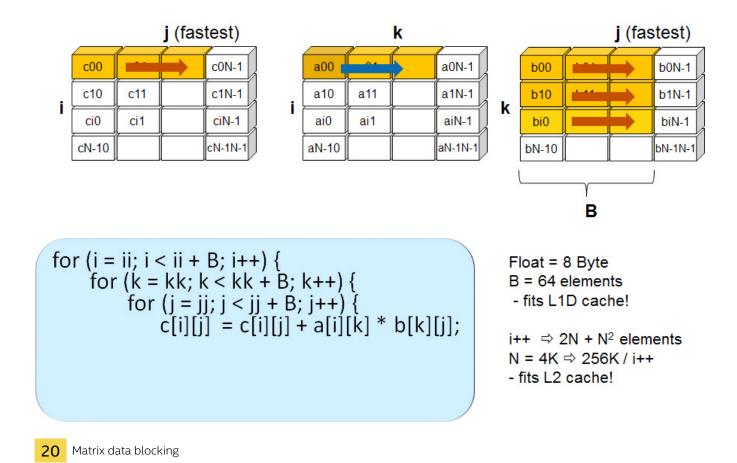

## **Data Blocking**

We can decrease the data latencies for eliminating CPU stalls by yet another modification of the multiplication algorithm. We want all data in the three matrixes being accessed by threads running on a local socket. One of the well-known and frequently used modifications is data blocking (Figure 20). It allows working with smaller blocks of arrays from each of the matrices, keeping them hot in caches and reused by CPU (which, in turn, gives opportunities for further performance improvements through optimizing the blocks for CPU cache sizes). Also, this makes it easier to distribute the blocks among threads and prevent massive remote accesses and reloads.

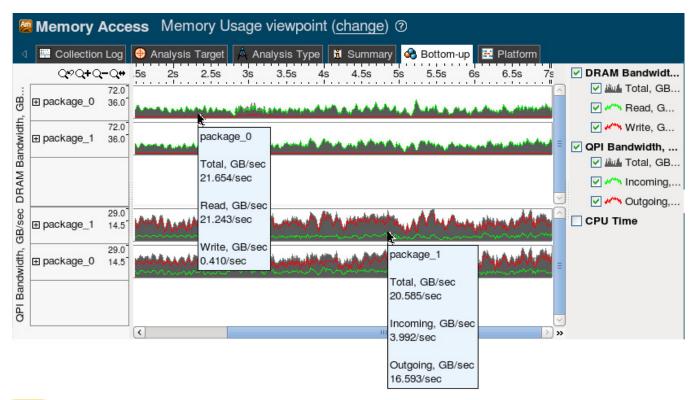

If we look at the results of the cache blocking modification (Figure 21), we can observe that even without fixing NUMA effects, memory latencies are much smaller and execution is much faster.

```

./matrix.icc

Threads #: 72 Pthreads

Matrix size: 9216

Using multiply kernel: multiply3

Freq = 2.3 GHz

Execution time = 12.08 seconds

MFLOPS: 128710.367 mflops

```

Cache blocking modification (multiply3)

According to the General Exploration profile (Figure 22), the Retiring pipeline slots increased up to 20 percent, while the rest of CPU stalls are shared between Memory Bound and Core Bound execution.

```

Clockticks:

2,268,184,100,000

Instructions Retired:

1,851,470,100,000

CPI Rate 12:

1.225

MUX Reliability ::

0.994

Front-End Bound <sup>②</sup>:

9.4%

of Pipeline Slots

Bad Speculation <sup>Q</sup>

0.0%

of Pipeline Slots

⊗ Back-End Bound <sup>③</sup>:

70.9%

of Pipeline Slots

Memory Bound <sup>□</sup>:

45.6% of Pipeline Slots

L1 Bound <sup>3</sup>:

0.7%

of Clockticks

L2 Bound (2):

5.6%

of Clockticks

✓ L3 Bound <sup>③</sup>:

31.9%

of Clockticks

Contested Accesses (2):

0.0%

of Clockticks

Data Sharing (2):

0.0%

of Clockticks

L3 Latency (2):

100.0%

of Clockticks

SQ Full (2):

0.0%

of Clockticks

3.0%

of Clockticks

Memory Bandwidth (1):

26.9%

of Clockticks

Memory Latency <sup>3</sup>:

69.5%

of Clockticks

Local DRAM (7):

36.6%

of Clockticks

Remote DRAM (3):

6.5%

of Clockticks

Remote Cache (1):

0.0%

of Clockticks

Store Bound ::

1.2%

of Clockticks

Ore Bound ::

25.3%

of Pipeline Slots

Retiring ":

19.6%

of Pipeline Slots

Total Thread Count:

73

Paused Time (2):

0s

```

22 General Exploration profile (multiply3)

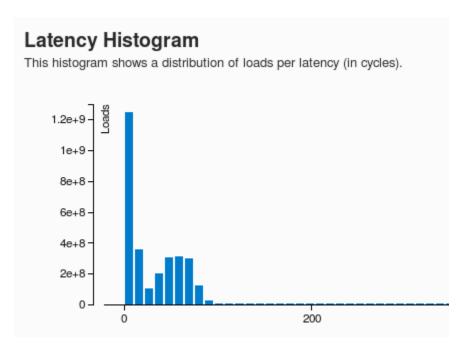

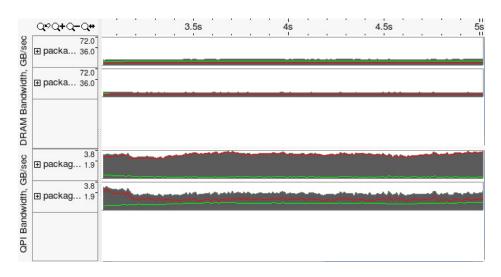

According to the Latency Histogram (**Figure 23**), most of the latencies are concentrated around L2 access values, while the rest are in the zone of 50 to 100 cycles, which is in the area of LLC Hit latency numbers. The Bandwidth timeline diagram (**Figure 24**) shows that most of data is taken from a local DRAM, and traffic on QPI is slightly increased. This is still a smaller performance than the **Intel® Math Kernel Library (Intel® MKL)** implementation of the double-precision matrix multiplication (dgemm), but closer to it for this size of matrix (**Figure 25**). So, the final optimization that we could do is modifying the algorithm to be blocked and fully NUMA aware. The final performance is shown in **Table 3** and **Figure 26**.

23 Latency histogram (multiply3)

24 Bandwidth timeline diagram (multiply3)

```

$./matrix.mkl

Threads #: 72 requested OpenMP threads

Matrix size: 9216

Using multiply kernel: multiply5

Freq = 2.799980 GHz

Execution time = 2.897 seconds

MFLOPS: 540032.936 mflops

```

Performance measurement for Intel® MKL-based multiply5

| No. Threads | Elapsed Time, Seconds | DP FLOPS, GFLOPS/Second |

|-------------|-----------------------|-------------------------|

| 4           | 104.8                 | 14                      |

| 8           | 60.1                  | 25                      |

| 16          | 31.3                  | 49                      |

| 36          | 17.85                 | 87                      |

| 72 HT       | 12.08                 | 128                     |

Table 3. Performance of the final matrix3 optimization (36 cores, Intel® Xeon® processor E5-2697 v4, two sockets @ 2300 MHz)

## **BLOG HIGHLIGHTS**

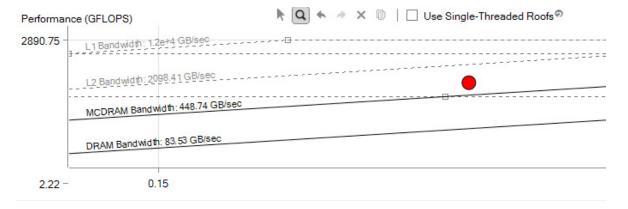

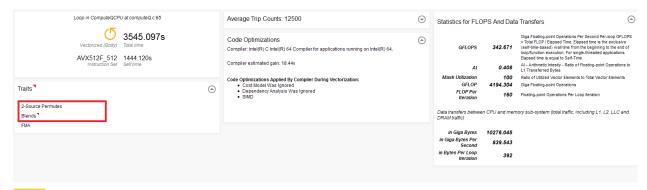

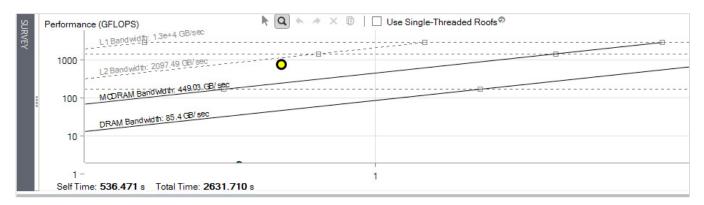

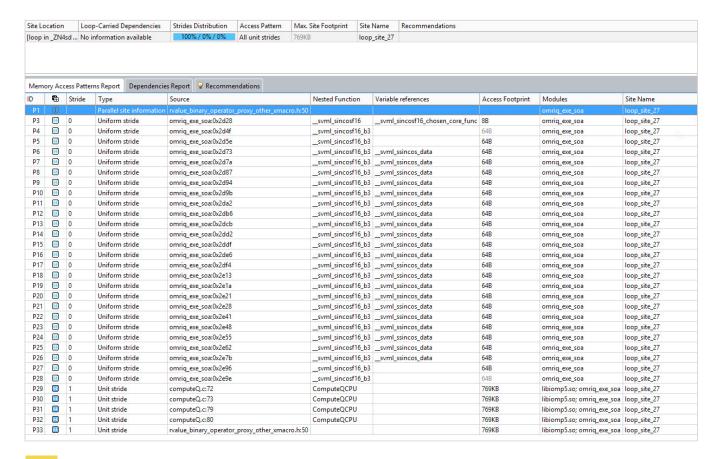

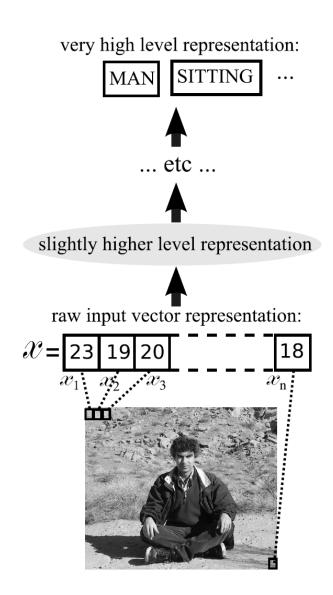

## How to Get Started as a Developer in AI

**BY NIVEN SINGH (INTEL) >**