# Hardware Assisted Virtualization Intel Virtualization Technology

Matías Zabaljáuregui matiasz@info.unlp.edu.ar

Buenos Aires, Junio de 2008

# Index

| 1        | Bac  | kgrour                        | nd, motivation and introduction to Intel Virtualiza     | L <b>-</b> |  |  |  |

|----------|------|-------------------------------|---------------------------------------------------------|------------|--|--|--|

|          | tion | Exter                         | nsions                                                  | 3          |  |  |  |

|          | 1.1  | Challe                        | nges to virtualizing Intel architecture                 | 3          |  |  |  |

|          |      | 1.1.1                         | Ring aliasing                                           | 3          |  |  |  |

|          |      | 1.1.2                         | Address-space compression                               | 3          |  |  |  |

|          |      | 1.1.3                         | Nonfaulting access to privileged state                  | 4          |  |  |  |

|          |      | 1.1.4                         | Adverse impacts on guest transitions                    | 5          |  |  |  |

|          |      | 1.1.5                         | Interrupt virtualization                                | 5          |  |  |  |

|          |      | 1.1.6                         | Ring compression                                        | 5          |  |  |  |

|          |      | 1.1.7                         | Access to hidden state                                  | 6          |  |  |  |

|          | 1.2  | Addre                         | ssing virtualization challenges in software             | 6          |  |  |  |

|          | 1.3  | 0.                            |                                                         |            |  |  |  |

|          |      | 1.3.1                         | Virtual Machine Architecture                            | 6          |  |  |  |

|          |      | 1.3.2                         | Introduction to VMX operation                           | 7          |  |  |  |

|          |      | 1.3.3                         | Life Cycle of VMM software                              | 7          |  |  |  |

|          |      | 1.3.4                         | Virtual Machine Control Structure                       |            |  |  |  |

|          |      | 1.3.5                         | Restrictions on VMX operation                           | 8          |  |  |  |

|          |      |                               |                                                         |            |  |  |  |

| <b>2</b> |      |                               | achine Control Structure                                | 9          |  |  |  |

|          | 2.1  | Overvi                        |                                                         | 9          |  |  |  |

|          | 2.2  |                               | t of the VMCS region                                    |            |  |  |  |

|          | 2.3  |                               | ization of VMCS data                                    | 10         |  |  |  |

|          | 2.4  | Guest-                        | State Area                                              | 10         |  |  |  |

|          |      | 2.4.1                         | Guest Register State                                    |            |  |  |  |

|          |      | 2.4.2                         | Guest Non-Register State                                |            |  |  |  |

|          | 2.5  | Host-State Area               |                                                         |            |  |  |  |

|          | 2.6  | 6 VM-Execution Control Fields |                                                         |            |  |  |  |

|          |      | 2.6.1                         | Pin-Based VM-Execution Controls                         |            |  |  |  |

|          |      | 2.6.2                         | Processor-Based VM-Execution Controls                   |            |  |  |  |

|          |      | 2.6.3                         | Exception Bitmap                                        |            |  |  |  |

|          |      | 2.6.4                         | I/O-Bitmap Addresses                                    |            |  |  |  |

|          |      | 2.6.5                         | Time-Stamp Counter Offset                               |            |  |  |  |

|          |      | 2.6.6                         | Guest/Host Masks and Read Shadows for CR0 and CR4 .     | 15         |  |  |  |

|          |      | 2.6.7                         | CR3-Target Controls                                     |            |  |  |  |

|          |      | 2.6.8                         | Controls for CR8 Accesses                               |            |  |  |  |

|          |      | 2.6.9                         | MSR-Bitmap Address                                      |            |  |  |  |

|          |      | 2.6.10                        | Executive-VMCS Pointer                                  | 17         |  |  |  |

|          | 2.7  | VM-E                          | xit Control Fields                                      | 17         |  |  |  |

|          |      | 2.7.1                         | VM-Exit Controls                                        | 17         |  |  |  |

|          |      | 2.7.2                         | VM-Exit Controls for MSRs                               | 17         |  |  |  |

|          | 2.8  | VM-E                          | ntry Control Fields                                     | 18         |  |  |  |

|          |      | 2.8.1                         | VM-Entry Controls                                       | 18         |  |  |  |

|          |      | 2.8.2                         | VM-Entry Controls for MSRs                              | 18         |  |  |  |

|          |      | 2.8.3                         | VM-Entry Controls for Event Injection                   | 18         |  |  |  |

|          | 2.9  | VM-E                          | xit Information Fields                                  | 19         |  |  |  |

|          |      | 2.9.1                         | Basic VM-Exit Information                               | 19         |  |  |  |

|          |      | 2.9.2                         | Information for VM Exits Due to Vectored Events         | 19         |  |  |  |

|          |      | 2.9.3                         | Information for VM Exits Due to Instruction Execution . | 20         |  |  |  |

| 3            | VMX non-root operation 20                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                         |  |  |

|--------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              | 3.1                                                  | Instructions that cause VM exits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20                                                                                                                                      |  |  |

|              |                                                      | 3.1.1 Instructions That Cause VM Exits Unconditionally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                                                                                                      |  |  |

|              |                                                      | 3.1.2 Instructions That Cause VM Exits Conditionally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                                                                                                      |  |  |

|              | 3.2                                                  | Other causes of VM exits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23                                                                                                                                      |  |  |

|              | 3.3                                                  | Changes to instruction behavior in VMX non-root operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                                                                                      |  |  |

|              | 3.4                                                  | Other Changes in VMX non-root operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28                                                                                                                                      |  |  |

|              |                                                      | 3.4.1 Event Blocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28                                                                                                                                      |  |  |

|              |                                                      | 3.4.2 Treatment of Task Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28                                                                                                                                      |  |  |

| 4            | Mei                                                  | mory Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29                                                                                                                                      |  |  |

| -            | 4.1                                                  | Processor Operating Modes & Memory Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29                                                                                                                                      |  |  |

|              | 4.2                                                  | Guest & Host Physical Address Spaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                                                                                      |  |  |

|              | 4.3                                                  | Virtualizing Virtual Memory by Brute Force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                                                                                                      |  |  |

|              | 4.4                                                  | Alternate Approach to Memory Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                                      |  |  |

|              | 4.4                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                                                                                      |  |  |

| <b>5</b>     | На                                                   | ndling interruptions in VMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>32</b>                                                                                                                               |  |  |

|              | 5.1                                                  | VMX support for handling interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32                                                                                                                                      |  |  |

|              | 5.2                                                  | External interrupt virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                                                                                                      |  |  |

|              |                                                      | 5.2.1 Virtualization of Interrupt Vector Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35                                                                                                                                      |  |  |

|              |                                                      | 5.2.2 Control of Platform Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37                                                                                                                                      |  |  |

|              |                                                      | 5.2.3 Examples of Handling of External Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39                                                                                                                                      |  |  |

|              |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                         |  |  |

|              |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                         |  |  |

| $\mathbf{A}$ | AP                                                   | PENDIX: First steps in programming a VMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42                                                                                                                                      |  |  |

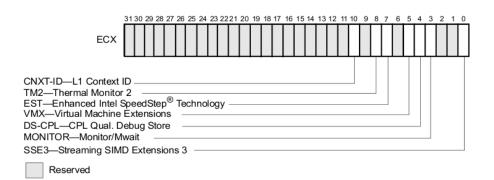

| Α            | <b>AP</b><br>A.1                                     | Discovering support for VMX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42                                                                                                                                      |  |  |

| Α            |                                                      | Discovering support for VMX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\begin{array}{c} 42 \\ 42 \end{array}$                                                                                                 |  |  |

| Α            | A.1                                                  | Discovering support for VMX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42<br>42<br>42                                                                                                                          |  |  |

| Α            | A.1<br>A.2                                           | Discovering support for VMX Enabling and entering VMX operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42<br>42<br>42<br>42                                                                                                                    |  |  |

| Α            | A.1<br>A.2                                           | Discovering support for VMX Enabling and entering VMX operation Software Access to the VMCS and related structures A.3.1 Software Access to the Virtual-Machine Control Structure A.3.2 VMREAD, VMWRITE, and Encodings of VMCS Fields .                                                                                                                                                                                                                                                                                                                                                                                         | 42<br>42<br>42<br>42<br>43                                                                                                              |  |  |

| Α            | A.1<br>A.2                                           | Discovering support for VMX Enabling and entering VMX operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42<br>42<br>42<br>42                                                                                                                    |  |  |

| Α            | A.1<br>A.2                                           | Discovering support for VMX Enabling and entering VMX operation Software Access to the VMCS and related structures A.3.1 Software Access to the Virtual-Machine Control Structure A.3.2 VMREAD, VMWRITE, and Encodings of VMCS Fields .                                                                                                                                                                                                                                                                                                                                                                                         | 42<br>42<br>42<br>42<br>43                                                                                                              |  |  |

| Α            | A.1<br>A.2                                           | Discovering support for VMX Enabling and entering VMX operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{c} 42 \\ 42 \\ 42 \\ 42 \\ 43 \\ 43 \end{array}$                                                                         |  |  |

| Α            | A.1<br>A.2                                           | Discovering support for VMX Enabling and entering VMX operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42<br>42<br>42<br>42<br>43<br>43<br>43                                                                                                  |  |  |

| A            | A.1<br>A.2                                           | Discovering support for VMX Enabling and entering VMX operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42<br>42<br>42<br>43<br>43<br>43<br>43<br>44                                                                                            |  |  |

| A            | A.1<br>A.2<br>A.3                                    | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS states                                                                                                                                                                                                                                                                        | 42<br>42<br>42<br>43<br>43<br>43<br>43<br>44<br>44                                                                                      |  |  |

| A            | A.1<br>A.2<br>A.3                                    | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest Execution                                                                                                                                                                                | $\begin{array}{c} 42 \\ 42 \\ 42 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44 \\$                                                                      |  |  |

| A            | A.1<br>A.2<br>A.3<br>A.4                             | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest ExecutionUsing VMX instructions                                                                                                                                                          | $\begin{array}{c} 42 \\ 42 \\ 42 \\ 42 \\ 43 \\ 43 \\ 43 \\ 44 \\ 44$                                                                   |  |  |

| A            | A.1<br>A.2<br>A.3<br>A.4<br>A.5                      | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest ExecutionUsing VMX instructionsVMM setup & tear down                                                                                                                                     | $\begin{array}{c} 42 \\ 42 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 45 \\ 46 \\ 46 \\ 46 \end{array}$                                     |  |  |

| A            | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6               | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest ExecutionUsing VMX instructionsVMM setup & tear downPreparation and launching a virtual machine                                                                                          | $\begin{array}{c} 42 \\ 42 \\ 42 \\ 43 \\ 43 \\ 43 \\ 43 \\ 44 \\ 45 \\ 46 \\ 46 \\ 46 \\ 46 \end{array}$                               |  |  |

| A            | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7        | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest ExecutionUsing VMX instructionsVMM setup & tear downPreparation and launching a virtual machineHandling of VM exits                                                                      | $\begin{array}{c} 42 \\ 42 \\ 42 \\ 42 \\ 43 \\ 43 \\ 43 \\ 44 \\ 45 \\ 46 \\ 46 \\ 46 \\ 47 \end{array}$                               |  |  |

| A            | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7        | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest ExecutionUsing VMX instructionsVMM setup & tear downPreparation and launching a virtual machineHandling of VM exitsA.8.1Handling VM Exits Due to Exceptions                              | $\begin{array}{c} 42\\ 42\\ 42\\ 43\\ 43\\ 43\\ 43\\ 44\\ 44\\ 45\\ 46\\ 46\\ 46\\ 46\\ 46\\ 47\\ 48\end{array}$                        |  |  |

| A            | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8 | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest ExecutionUsing VMX instructionsVMM setup & tear downPreparation and launching a virtual machineHandling of VM exitsA.8.1Handling VM Exits Due to ExceptionsMultiprocessor considerations | $\begin{array}{c} 42\\ 42\\ 42\\ 42\\ 43\\ 43\\ 43\\ 43\\ 44\\ 44\\ 45\\ 46\\ 46\\ 46\\ 46\\ 46\\ 46\\ 47\\ 48\\ 49\\ 50\\ \end{array}$ |  |  |

| Α            | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8 | Discovering support for VMXEnabling and entering VMX operationSoftware Access to the VMCS and related structuresA.3.1Software Access to the Virtual-Machine Control StructureA.3.2VMREAD, VMWRITE, and Encodings of VMCS FieldsA.3.3Software Access to Related StructuresA.3.4VMXON RegionA.3.5Using VMCLEAR to initialize a VMCS regionA.3.6VMCS statesSupporting processor operating modes in guest invironmentsA.4.1Emulating Guest ExecutionUsing VMX instructionsVMM setup & tear downPreparation and launching a virtual machineHandling of VM exitsA.8.1Handling VM Exits Due to Exceptions                              | $\begin{array}{c} 42\\ 42\\ 42\\ 42\\ 43\\ 43\\ 43\\ 43\\ 44\\ 45\\ 46\\ 46\\ 46\\ 46\\ 46\\ 46\\ 46\\ 46\\ 48\\ 49\end{array}$         |  |  |

# 1 Background, motivation and introduction to Intel Virtualization Extensions

#### 1.1 Challenges to virtualizing Intel architecture

Established and emerging applications motivate strong support for virtualization in both server and client computing systems. Unfortunately, the IA-32 and Itanium architectures impose many challenges to providing such support. Software techniques exist that address some of those challenges.

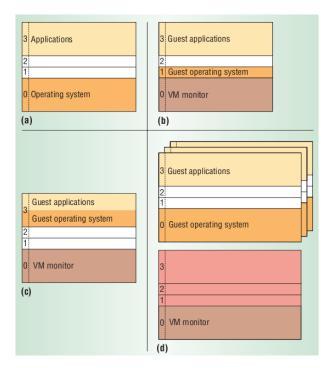

Intel microprocessors provide protection based on the concept of a 2-bit privilege level, using 0 for most-privileged software and 3 for the least privileged. The privilege level determines whether privileged instructions, which control basic CPU functionality, can execute without fault; it also controls address-space accessibility based on the configuration of the processor's page tables and, for IA-32, segment registers. Most IA software uses only privilege levels 0 and 3, as Figure 1a illustrates. For an OS to control the CPU, some of its components must run with privilege level 0. Because a VMM cannot allow a guest OS such control, a guest OS cannot execute at privilege level 0. Thus, IA-based VMMs must use ring deprivileging, a technique that runs all guest software at a privilege level greater than 0. A VM could deprivilege a guest OS by running it either at privilege level 1 (the 0/1/3 model) or at privilege level 3 (the 0/3/3 model).

Figures 1b and 1c illustrate these choices. Although the 0/1/3 model supports simpler VMMs, it cannot be used on IA-32 processors for guests in 64-bit mode. The 64-bit mode is part of Intel's EM64T (Extended Memory 64 Technology), the 64-bit extension to IA-32. Ring deprivileging causes numerous virtualization challenges. Intel virtual technology extensions (vt-x) solve virtualization challenges in part by allowing guest software to run at its intended privilege level. Guest software is constrained, not by privilege level, but because —for VT-x— it runs in VMX non-root operation. Figure 1d illustrates this usage.

#### 1.1.1 Ring aliasing

Ring aliasing refers to problems that arise when software is run at a privilege level other than the level for which it was written. An example in IA-32 is the PUSH instruction (which pushes its operand on the stack) when executed with the CS register (part of which is the current privilege level). A guest OS could easily determine that it is not running at privilege level 0.

#### 1.1.2 Address-space compression

Operating systems expect to have access to the processor's full virtual address space, known as the linear-address space in IA-32. A VMM must reserve for itself some portion of the guest's virtual-address space. The VMM could run entirely within the guest's virtual-address space, which allows it easy access to guest data, although the VMM's instructions and data structures might use a substantial amount of the guest's virtual-address space. Alternatively, the VMM could run in a separate address space, but even in that case the VMM must use a minimal amount of the guest's virtual-address space for the control structures

Figure 1: rings rings rings

that manage transitions between guest software and the VMM. (For IA-32, these structures include the IDT and the GDT, which reside in the linear-address space.) The VMM must prevent guest access to those portions of the guest's virtual-address space that the VMM is using. Otherwise, the VMM's integrity could be compromised if the guest can write to those portions, or the guest could detect that it is running in a virtual machine if it can read them. Guest attempts to access these portions of the address space must generate transitions to the VMM, which can emulate or otherwise support them. The term address space compression refers to the challenges of protecting these portions of the virtual-address space and supporting guest accesses to them.

#### 1.1.3 Nonfaulting access to privileged state

Privilege-based protection prevents unprivileged software from accessing certain components of CPU state. In most cases, attempted accesses result in faults, allowing a VMM to emulate the desired guest instruction. However, the IA-32 architecture includes instructions that access privileged state and do not fault when executed with insufficient privilege. For example, the IA-32 registers GDTR, IDTR, LDTR, and TR contain pointers to data structures that control CPU operation. Software can execute the instructions that write to, or load, these registers (LGDT, LIDT, LLDT, and LTR) only at privilege level 0. However, software can execute the instructions that read, or store, from these registers (SGDT, SIDT, SLDT, and STR) at any privilege level. If the VMM maintains these registers with unexpected values, a guest OS using the latter instructions could determine that it does not have full control of the CPU.

#### 1.1.4 Adverse impacts on guest transitions

Ring deprivileging can interfere with the effectiveness of facilities in the IA-32 architecture that accelerate the delivery and handling of transitions to OS software. The IA-32 SYSENTER and SYSEXIT instructions support low-latency system calls. SYSENTER always effects a transition to privilege level 0, and SYSEXIT will fault if executed outside that privilege level. Ring deprivileging thus has the following implications:

- Executions of SYSENTER by a guest application will cause a transition to the VMM and not to the guest OS. The VMM must thus emulate every guest execution of SYSENTER.

- Execution of SYSEXIT by a guest OS will cause a fault to the VMM. Thus, the VMM must emulate every guest execution of SYSEXIT.

#### 1.1.5 Interrupt virtualization

Providing support for external interrupts, especially regarding interrupt masking, presents some specific challenges to VMM design. The IA-32 architecture provides mechanisms for masking external interrupts, preventing their delivery when the OS is not ready for them. IA-32 uses the interrupt flag (IF) in the EFLAGS register to control interrupt masking. A VMM will likely manage external interrupts and deny guest software the ability to control interrupt masking. Existing protection mechanisms allow such denial of control by ensuring that guest attempts to control interrupt masking will fault in the context of ring deprivileging. Such faulting can cause problems because some operating systems frequently mask and unmask interrupts. Intercepting every guest attempt to do so could significantly affect system performance.

Even if it were possible to prevent guest modifications of interrupt masking without intercepting each attempt, challenges would remain when a VMM has a "virtual interrupt" to deliver to a guest. A virtual interrupt should be delivered only when the guest has unmasked interrupts. To deliver virtual interrupts in a timely way, a VMM should intercept some, but not all, attempts by a guest to modify interrupt masking. Doing so could signicantly complicate the design of a VMM.

#### 1.1.6 Ring compression

Ring deprivileging uses translation privilege-based mechanisms to protect the VMM from guest software. IA-32 includes two such mechanisms: segment limits and paging. Because segment limits do not apply in 64-bit mode, paging must be used in this mode. Because IA-32 paging does not distinguish privilege levels 0-2, the guest OS must run at privilege level 3. Thus, the guest OS will run at the same privilege level as guest applications and will not be protected from them. This problem is called ring compression.

#### 1.1.7 Access to hidden state

Some components of IA-32 CPU state are not represented in any softwareaccessible register. Examples include the hidden descriptor caches for the segment registers. A segment-register load copies a referenced descriptor (from the GDT or LDT) into this cache, which is not modified if software later writes to the descriptor tables. IA-32 does not provide mechanisms for saving and restoring these hidden components of a guest context when changing VMs or for preserving them while the VMM is running.

## 1.2 Addressing virtualization challenges in software

To address the virtualization challenges that the IA-32 architecture presents, VMM designers have developed creative solutions that modify guest software (source or binary). There are examples of VMMs that use sourcelevel modifiations in a technique called paravirtualization. Developers of these VMMs modify a guest-OS kernel and its device drivers to create an interface that is easier to virtualize. Paravirtualization offers high performance and does not require making changes to guest applications. A disadvantage of paravirtualization is that it limits the range of supported operating systems. For example, Xen cannot currently support an operating system that its developers have not modified, such as Microsoft Windows.

A VMM can support legacy operating systems by making modifications directly to guest-OS binaries. VMMs that use such binary translation techniques include those developed by VMware as well as Virtual PC and Virtual Server from Microsoft. Such VMMs support a broader range of operating systems, albeit with higher performance overheads, than VMMs that use paravirtualization.

A central design goal for Intel Virtualization Technology is to eliminate the need for CPU paravirtualization and binary translation techniques and thereby enable the implementation of VMMs that can support a broad range of unmodified guest operating systems while maintaining high levels of performance.

## **1.3** Intel Virtualization Technology

This section describes the basics of virtual machine architecture and an overview of the virtual-machine extensions (VMX) that support virtualization of processor hardware for multiple software environments.

#### 1.3.1 Virtual Machine Architecture

Virtual-machine extensions define processor-level support for virtual machines on IA-32 processors. Two principal classes of software are supported:

• Virtual-machine monitors (VMM): A VMM acts as a host and has full control of the processor(s) and other platform hardware. A VMM presents guest software (see next paragraph) with an abstraction of a virtual processor and allows it to execute directly on a logical processor. A VMM is able to retain selective control of processor resources, physical memory, interrupt management, and I/O. • Guest software: Each virtual machine (VM) is a guest software environment that supports a stack consisting of operating system (OS) and application software. Each operates independently of other virtual machines and uses on the same interface to processor(s), memory, storage, graphics, and I/O provided by a physical platform. The software stack acts as if it were running on a platform with no VMM. Software executing in a virtual machine must operate with reduced privilege so that the VMM can retain control of platform resources.

#### 1.3.2 Introduction to VMX operation

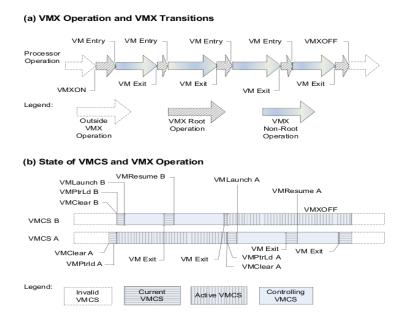

Processor support for virtualization is provided by a form of processor operation called VMX operation. There are two kinds of VMX operation: VMX root operation and VMX non-root operation. In general, a VMM will run in VMX root operation and guest software will run in VMX non-root operation. Transitions between VMX root operation and VMX non-root operation are called VMX transitions. There are two kinds of VMX transitions. Transitions into VMX non-root operation are called VM entries. Transitions from VMX non-root operation to VMX root operation are called VM exits.

Processor behavior in VMX root operation is very much as it is outside VMX operation. The principal differences are that a set of new instructions (the VMX instructions) is available and that the values that can be loaded into certain control registers are limited.

Processor behavior in VMX non-root operation is restricted and modified to facilitate virtualization. Instead of their ordinary operation, certain instructions (including the new VMCALL instruction) and events cause VM exits to the VMM. Because these VM exits replace ordinary behavior, the functionality of software in VMX non-root operation is limited. It is this limitation that allows the VMM to retain control of processor resources. There is no software-visible bit whose setting indicates whether a logical processor is in VMX non-root operation. This fact may allow a VMM to prevent guest software from determining that it is running in a virtual machine. Because VMX operation places restrictions even on software running with current privilege level (CPL) 0, guest software can run at the privilege level for which it was originally designed. This capability may simplify the development of a VMM.

#### 1.3.3 Life Cycle of VMM software

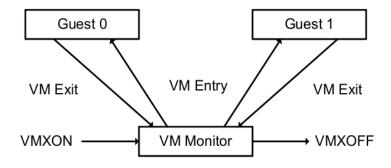

Figure 2 illustrates the life cycle of a VMM and its guest software as well as the interactions between them. The following items summarize that life cycle:

- Software enters VMX operation by executing a VMXON instruction.

- Using VM entries, a VMM can then enter guests into virtual machines (one at a time). The VMM effects a VM entry using instructions VMLAUNCH and VMRESUME; it regains control using VM exits.

- VM exits transfer control to an entry point specified by the VMM. The VMM can take action appropriate to the cause of the VM exit and can then return to the virtual machine using a VM entry.

Figure 2: Interaction of a Virtual-Machine Monitor and Guests

• Eventually, the VMM may decide to shut itself down and leave VMX operation. It does so by executing the VMXOFF instruction.

## 1.3.4 Virtual Machine Control Structure

VMX non-root operation and VMX transitions are controlled by a data structure called a virtual-machine control structure (VMCS). Access to the VMCS is managed through a component of processor state called the VMCS pointer (one per logical processor). The value of the VMCS pointer is the 64-bit address of the VMCS. The VMCS pointer is read and written using the instructions VMPTRST and VMPTRLD. The VMM configures a VMCS using the VM-READ, VMWRITE, and VMCLEAR instructions. A VMM could use a different VMCS for each virtual machine that it supports. For a virtual machine with multiple logical processors (virtual processors), the VMM could use a different VMCS for each virtual processor.

#### 1.3.5 Restrictions on VMX operation

VMX operation places restrictions on processor operation. These are detailed below:

• In VMX operation, processors may fix certain bits in CR0 and CR4 to specific values and not support other values. VMXON fails if any of these bits contains an unsupported value. Any attempt to set one of these bits to an unsupported value while in VMX operation (including VMX root operation) using any of the CLTS, LMSW, or MOV CR instructions causes a general-protection exception. VM entry or VM exit cannot set any of these bits to an unsupported value.(2)

NOTE The first processors to support VMX operation require that the following bits be 1 in VMX operation: CR0.PE, CR0.NE, CR0.PG, and CR4.VMXE. The restrictions on CR0.PE and CR0.PG imply that VMX operation is supported only in paged protected mode (including IA-32e mode). Therefore, guest software cannot be run in unpaged protected

mode or in real-address mode natively. But there are techniques to support these kind of guests with vt-x.

- VMXON fails if a logical processor is in A20M mode. Once the processor is in VMX operation, A20M interrupts are blocked. Thus, it is impossible to be in A20M mode in VMX operation.

- The INIT signal is blocked whenever a logical processor is in VMX root operation. It is not blocked in VMX non-root operation. Instead, INITs cause VM exits.

# 2 Virtual Machine Control Structure

#### 2.1 Overview

The virtual-machine control data structure (VMCS) is defined for VMX operation. A VMCS manages transitions in and out of VMX non-root operation (VM entries and VM exits) as well as processor behavior in VMX non-root operation. This structure is manipulated by the new instructions VMCLEAR, VMPTRLD, VMREAD, and VMWRITE.

A VMM can use a different VMCS for each virtual machine that it supports. For a virtual machine with multiple logical processors (virtual processors), the VMM can use a different VMCS for each virtual processor. Each logical processor associates a region in memory with each VMCS. This region is called the VMCS region. Software references a specific VMCS by using the 64-bit physical address of the region; such an address is called a VMCS pointer. VMCS pointers must be aligned on a 4-KByte boundary (bits 11:0 must be zero). A logical processor may maintain any number of active VMCSs. At any given time, one is the current VMCS:

- Software makes a VMCS active by executing VMPTRLD with the address of the VMCS. The processor may optimize VMX operation by maintaining the state of an active VMCS in memory, on the processor, or both. Software should not make a VMCS active on more than one logical processor. Software makes a VMCS inactive by executing VMCLEAR with the address of the VMCS. A logical processor does not use an inactive VMCS or maintain its state on the processor.

- Software makes a VMCS current by executing VMPTRLD with the address of the VMCS; that address is loaded into the current-VMCS pointer. VMX instructions VMLAUNCH, VMPTRST, VMREAD, VMRESUME, and VMWRITE operate on the current VMCS. A VMCS remains current until either software executes VMPTRLD with the address of a different VMCS (which then becomes the current VMCS) or software executes VM-CLEAR with the address of the current VMCS (after which there is no current VMCS).

NOTE: This document uses the notation RAX, RIP, RSP, RFLAGS, etc. for processor registers because most processors that support VMX operation also support Intel 64 architecture. For processors that do not support Intel 64 architecture, this notation refers to the 32-bit forms of those registers (EAX, EIP, ESP, EFLAGS, etc.).

#### 2.2 Format of the VMCS region

A VMCS region comprises up to 4-KBytes.

The first 32 bits of the VMCS region contain the VMCS revision identifier. Processors that maintain VMCS data in different formats use different VMCS revision identifiers. These identifiers enable software to avoid using a VMCS region formatted for one processor on a processor that uses a different format. Software should write the VMCS revision identifier to the VMCS region before using that region for a VMCS. The VMCS revision identifier is never written by the processor; VMPTRLD may fail if its operand references a VMCS region whose VMCS revision identifier differs from that used by the processor. Software can discover the VMCS revision identifier that a processor uses by reading the VMX capability MSR IA32\_VMX\_BASIC.

The next 32 bits of the VMCS region are used for the VMX-abort indicator. The contents of these bits do not control processor operation in any way. A logical processor writes a non-zero value into these bits if a VMX abort occurs. Software may also write into this field.

The remainder of the VMCS region is used for VMCS data (those parts of the VMCS that control VMX non-root operation and the VMX transitions). The format of these data is implementation-specific. To ensure proper behavior in VMX operation, software should maintain the VMCS region and related structures in writeback cacheable memory. Future implementations may allow or require a different memory type. Software should consult the VMX capability MSR IA32\_VMX\_BASIC.

## 2.3 Organization of VMCS data

The VMCS data are organized into six logical groups:

- Guest-state area. Processor state is saved into the guest-state area on VM exits and loaded from there on VM entries.

- Host-state area. Processor state is loaded from the host-state area on VM exits.

- VM-execution control fields. These fields control processor behavior in VMX non-root operation. They determine in part the causes of VM exits.

- VM-exit control fields. These fields control VM exits.

- VM-entry control fields. These fields control VM entries.

- VM-exit information fields. These fields receive information on VM exits and describe the cause and the nature of VM exits. They are read-only.

The VM-execution control fields, the VM-exit control fields, and the VMentry control fields are sometimes referred to collectively as VMX controls.

## 2.4 Guest-State Area

This section describes fields contained in the guest-state area of the VMCS. As noted earlier, processor state is loaded from these fields on every VM entry and stored into these fields on every VM exit.

#### 2.4.1 Guest Register State

The following fields in the guest-state area correspond to processor registers:

- Control registers CR0, CR3, and CR4 (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- Debug register DR7 (64 bits; 32 bits on processors that do not support Intel 64 architecture).

- RSP, RIP, and RFLAGS (64 bits each; 32 bits on processors that do not support Intel 64 architecture).5

- The following fields for each of the registers CS, SS, DS, ES, FS, GS, LDTR, and TR:

- Selector (16 bits).

- Base address (64 bits; 32 bits on processors that do not support Intel 64 architecture). The base-address fields for CS, SS, DS, and ES have only 32 architecturally-defined bits; nevertheless, the corresponding VMCS fields have 64 bits on processors that support Intel 64 architecture.

- Segment limit (32 bits). The limit field is always a measure in bytes.

- Access rights (32 bits). The format of this field is given in Table 20-2 and detailed as follows:

The base address, segment limit, and access rights compose the "hidden" part (or "descriptor cache") of each segment register. These data are included in the VMCS because it is possible for a segment register's descriptor cache to be inconsistent with the segment descriptor in memory (in the GDT or the LDT) referenced by the segment register's selector. Note that the value of the DPL field for SS is always equal to the logical processor's current privilege level (CPL).

- The following fields for each of the registers GDTR and IDTR:

- Base address (64 bits; 32 bits on processors that do not support Intel 64 architecture).

- Limit (32 bits). The limit fields contain 32 bits even though these fields are specified as only 16 bits in the architecture.

- The following MSRs:

- IA32\_DEBUGCTL (64 bits)

- IA32\_SYSENTER\_CS (32 bits)

- IA32\_SYSENTER\_ESP and IA32\_SYSENTER\_EIP (64 bits; 32 bits on processors that do not support Intel 64 architecture)

- The register SMBASE (32 bits). This register contains the base address of the logical processor's SMRAM image.

#### 2.4.2 Guest Non-Register State

In addition to the register state just described, the guest-state area includes the following fields that characterize guest state but which do not correspond to processor registers:

- Activity state (32 bits). This field identifies the logical processor's activity state. When a logical processor is executing instructions normally, it is in the active state. Execution of certain instructions and the occurrence of certain events may cause a logical processor to transition to an inactive state in which it ceases to execute instructions. The following activity states are defined: (8)

- 1. Active. The logical processor is executing instructions normally.

- 2. HLT. The logical processor is inactive because it executed the HLT instruction.

- 3. Shutdown. The logical processor is inactive because it incurred a triple fault (9) or some other serious error.

- 4. Wait-for-SIPI. The logical processor is inactive because it is waiting for a startup-IPI (SIPI).

- Interruptibility state (32 bits). The IA-32 architecture includes features that permit certain events to be blocked for a period of time. For example, execution of STI with RFLAGS.IF = 0 blocks interrupts (and, optionally, other events) for one instruction after its execution. Another example is that execution of a MOV to SS or a POP to SS blocks interrupts for one instruction after its execution. This field contains information about such blocking.

- Pending debug exceptions (64 bits; 32 bits on processors that do not support Intel 64 architecture). IA-32 processors may recognize one or more debug exceptions without immediately delivering them. This field contains information about such exceptions.

## 2.5 Host-State Area

This section describes fields contained in the host-state area of the VMCS. As noted earlier, processor state is loaded from these fields on every VM exit. All fields in the host-state area correspond to processor registers:

- CR0, CR3, and CR4 (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- RSP and RIP (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- Selector fields (16 bits each) for the segment registers CS, SS, DS, ES, FS, GS, and TR. There is no field in the host-state area for the LDTR selector.

- Base-address fields for FS, GS, TR, GDTR, and IDTR (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- The following MSRs:

- IA32\_SYSENTER\_CS (32 bits)

- IA32\_SYSENTER\_ESP and IA32\_SYSENTER\_EIP (64 bits; 32 bits on processors that do not support Intel 64 architecture).

In addition to the state identified here, some processor state components are loaded with fixed values on every VM exit; there are no fields corresponding to these components in the host-state area.

## 2.6 VM-Execution Control Fields

The VM-execution control fields govern VMX non-root operation.

#### 2.6.1 Pin-Based VM-Execution Controls

The pin-based VM-execution controls constitute a 32-bit vector that governs the handling of asynchronous events like interrupts (some asynchronous events cause VM exits regardless of the settings of the pin-based VM-execution controls). For example, if the field named "External-interrupt exiting" is 1, external interrupts cause VM exits. Otherwise, they are delivered normally through the guest interrupt-descriptor table (IDT). If this control is 1, the value of RFLAGS.IF does not affect interrupt blocking.

The other two controls are related with NMIs and Virtual NMIs

#### 2.6.2 Processor-Based VM-Execution Controls

The processor-based VM-execution controls constitute a 32-bit vector that governs the handling of synchronous events, mainly those caused by the execution of specific instructions<sup>1</sup>.

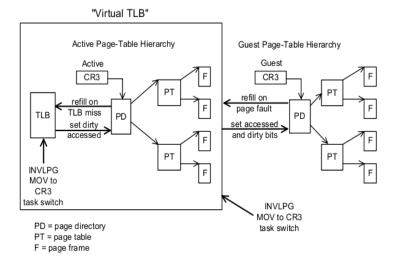

This control fields allow a VMM the flexibility to specify the instructions that cause VM exits. There are separate controls for each of the following instructions: HLT, INVLPG, MOV CR8, MOV DR, MWAIT, RDPMC, and RDTSC. These controls support a variety of virtualization strategies. It also includes the "use I/O bitmaps" and "use MSR bitmaps" fields, which indicates the use of these control bitmaps, and a "use TRP shadow" field which activates a shadow TRP maintained in a page of memory addressed by the virtual APIC address. See figure 3 for more details.

## 2.6.3 Exception Bitmap

The exception bitmap is a 32-bit field that contains one bit for each exception. When an exception occurs, its vector is used to select a bit in this field. If the bit is 1, the exception causes a VM exit. If the bit is 0, the exception is delivered normally through the IDT, using the descriptor corresponding to the exception's vector.

$<sup>^1 \</sup>rm Some$  instructions cause VM exits regardless of the settings of the processor-based VM-execution controls, as do task switches.

| Bit Position(s) | Name                         | Description                                                                                                                                                                                                       |

|-----------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2               | Interrupt-window<br>exiting  | If this control is 1, a VM exit occurs at the beginning of any instruction if RFLAGS.IF = 1 and there are no other blocking of interrupts (see Section 20.4.2).                                                   |

| 3               | Use TSC offsetting           | This control determines whether executions of RDTSC and executions of RDMSR that read from the IA32_TIME_STAMP_COUNTER MSR return a value modified by the TSC offset field (see Section 20.6.5 and Section 21.3). |

| 7               | HLT exiting                  | This control determines whether executions of HLT cause VM exits.                                                                                                                                                 |

| 9               | INVLPG exiting               | This determines whether executions of INVLPG cause VM exits.                                                                                                                                                      |

| 10              | MWAIT exiting                | This control determines whether executions of MWAIT cause VM exits.                                                                                                                                               |

| 11              | RDPMC exiting                | This control determines whether executions of RDPMC cause VM exits.                                                                                                                                               |

| 12              | RDTSC exiting                | This control determines whether executions of RDTSC cause VM exits.                                                                                                                                               |

| 19              | CR8-load exiting             | This control determines whether executions of MOV to CR8 cause VM exits. This control must be 0 on processors that do not support Intel 64 architecture.                                                          |

| 20              | CR8-store exiting            | This control determines whether executions of MOV from CR8 cause VM exits. This control must be 0 on processors that do not support Intel 64 architecture.                                                        |

| 21              | Use TPR shadow               | Setting this control to 1 activates the TPR shadow, which is maintained in a page of memory addressed by the virtual-APIC address. See Section 21.3.                                                              |

|                 |                              | This control must be 0 on processors that do not support<br>Intel 64 architecture.                                                                                                                                |

| 22              | NMI-window<br>exiting        | If this control is 1, a VM exit occurs at the beginning of any instruction if there is no virtual-NMI blocking (see Section 20.4.2).                                                                              |

|                 |                              | This control can be set only if the "virtual NMIs" VM-<br>execution control (see Section 20.6.1) is 1.                                                                                                            |

| 23              | MOV-DR exiting               | This control determines whether executions of MOV DR cause VM exits.                                                                                                                                              |

| 24              | Unconditional I/O<br>exiting | This control determines whether executions of I/O instructions (IN, INS/INSB/INSW/INSD, OUT, and OUTS/OUTSB/OUTSW/OUTSD) cause VM exits.                                                                          |

|                 |                              | This control is ignored if the "use I/O bitmaps" control is 1.                                                                                                                                                    |

| 25              | Use I/O bitmaps              | This control determines whether I/O bitmaps are used to restrict executions of I/O instructions (see Section 20.6.4 and Section 21.1.3).                                                                          |

|                 |                              | For this control, "O" means "do not use I/O bitmaps" and "1"<br>means "use I/O bitmaps." If the I/O bitmaps are used, the<br>setting of the "unconditional I/O exiting" control is ignored.                       |

| 28              | Use MSR bitmaps              | This control determines whether MSR bitmaps are used to control execution of the RDMSR and WRMSR instructions (see Section 20.6.4 and Section 21.1.3).                                                            |

|                 |                              | For this control, "0" means "do not use MSR bitmaps" and "1" means "use MSR bitmaps." If the MSR bitmaps are not used, all executions of the RDMSR and WRMSR instructions cause VM exits.                         |

|                 |                              | Not all processors support the 1-setting of this control.<br>Software may consult the VMX capability MSR<br>IA32_VMX_PROCBASED_CTLS (see Appendix G.2) to<br>determine whether that setting is supported.         |

| 29              | MONITOR exiting              | This control determines whether executions of MONITOR cause VM exits.                                                                                                                                             |

| 30              | PAUSE exiting                | This control determines whether executions of PAUSE cause VM exits.                                                                                                                                               |

Figure 3: Definitions of Processor-Based VM-Execution Controls

Whether a page fault (exception with vector 14) causes a VM exit is determined by bit 14 in the exception bitmap as well as the error code produced by the page fault and two 32-bit fields in the VMCS (the page-fault error-code mask and pagefault error-code match). See section 3 for details.

## 2.6.4 I/O-Bitmap Addresses

The VM-execution control fields include the 64-bit physical addresses of I/O bitmaps A and B (each of which are 4 KBytes in size). I/O bitmap A contains one bit for each I/O port in the range 0000H through 7FFFH; I/O bitmap B contains bits for ports in the range 8000H through FFFFH. A logical processor uses these bitmaps if and only if the "use I/O bitmaps" control is 1. If the bitmaps are used, execution of an I/O instruction causes a VM exit if any bit in the I/O bitmaps corresponding to a port it accesses is 1.

## 2.6.5 Time-Stamp Counter Offset

VM-execution control fields include a 64-bit TSC-offset field. If the "RDTSC exiting" control is 0 and the "use TSC offsetting" control is 1, this field controls executions of the RDTSC instruction and executions of the RDMSR instruction that read from the IA32\_TIME\_STAMP\_COUNTER MSR. The signed value of the TSC offset is combined with the contents of the time-stamp counter (using signed addition) and the sum is reported to guest software in EDX:EAX.

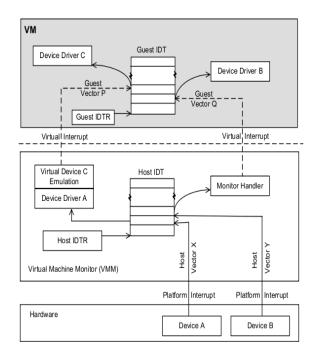

#### 2.6.6 Guest/Host Masks and Read Shadows for CR0 and CR4