# THE PARALLEL UNIVERSE

### Improve Productivity and Boost C++ Performance

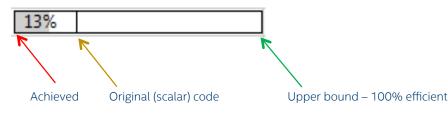

Intel<sup>®</sup> C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology

OpenMP\* API Version 4.5: A Standard Evolves

# CONTENTS

FEATURE FEATURE

| Letter from the Editor<br>Time-Saving Tips as Spring Begins in the Northern Hemisphere<br>by James Reinders                                                                                                                                                                               | 4  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Improve Productivity and Boost C++ Performance</b><br>The new Intel <sup>®</sup> SIMD Data Layout Template library optimizes C++ code and helps improve SIMD efficiency.                                                                                                               | 5  |

| Intel® C++ Compiler Standard Edition for<br>Embedded Systems with Bi-Endian Technology<br>Intel® C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology helps<br>developers looking to overcome platform lock-in.                                                   | 11 |

| <b>OpenMP* API Version 4.5: A Standard Evolves</b><br>OpenMP* version 4.5 is the next step in the standard's evolution, introducing new<br>concepts for parallel programming as well as additional features for offload programming.                                                      | 23 |

| <b>Intel® MPI Library: Supporting the Hadoop* Ecosystem</b><br>With data analytics breaking into the HPC world, the question of using MPI and big data<br>frameworks in the same ecosystem is getting more attention.                                                                     | 32 |

| <b>Finding Your Memory Access Performance Bottlenecks</b><br>The new Intel VTune Amplifier XE Memory Access analysis feature shows how some tough<br>memory problems can be resolved.                                                                                                     | 42 |

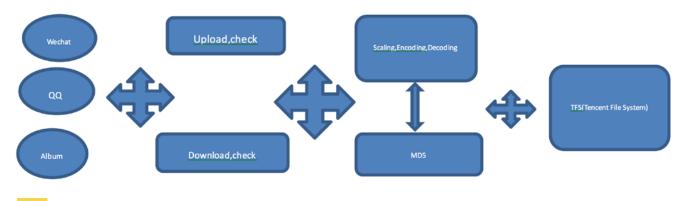

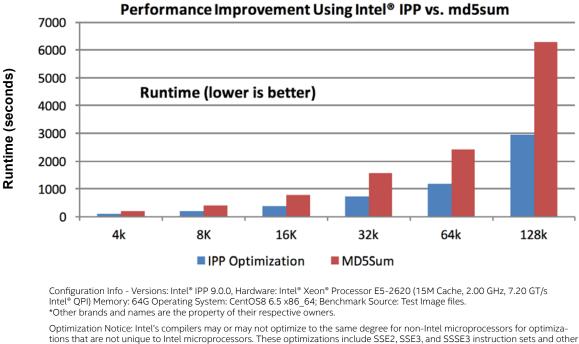

| Optimizing Image Identification with<br>Intel® Integrated Performance Primitives<br>Intel worked closely with engineers at China's largest and most-used Internet service portal to help<br>them achieve a 100 percent performance improvement on the Intel® architecture-based platform. | 62 |

# CONTENTS CONT....

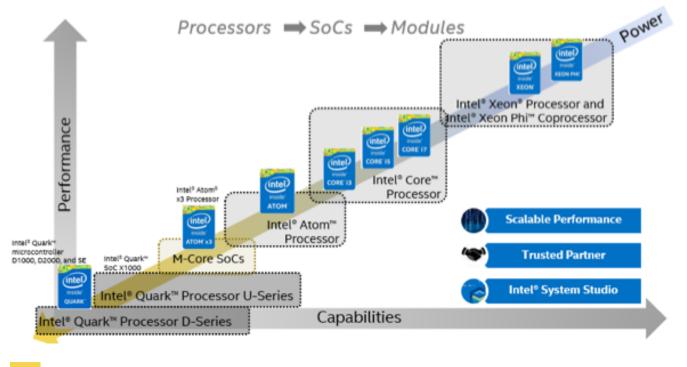

| <b>Develop Smarter Using the Latest IoT and Embedded Technology</b><br>A closer look at tools for coding, analysis, and debugging with all Intel® microcontrollers,<br>Internet of Things (IoT) devices, and embedded platforms. |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

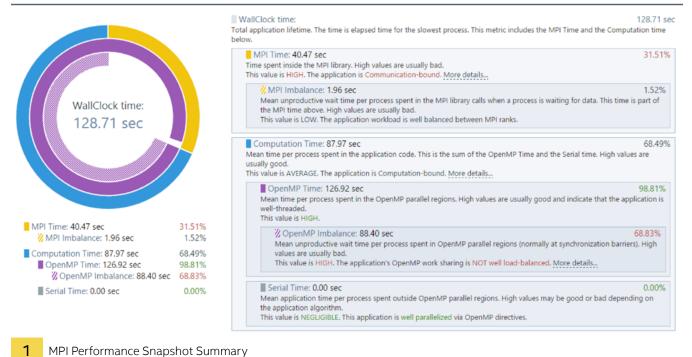

| <b>Tuning Hybrid Applications with Intel® Cluster Tools</b><br>This article provides a step-by-step workflow for hybrid application analysis and tuning.                                                                         | 79 |

| Vectorize Your Code Using Intel <sup>®</sup> Advisor XE 2016<br>Vectorization Advisor boasts new features that can assist with vectorization on the next<br>generation of Intel <sup>®</sup> Xeon Phi.                           | 89 |

### **LETTER FROM THE EDITOR**

James Reinders, an expert on parallel programming, is coeditor of the recent High Performance Parallel Programming Pearls Volumes One and Two. His other book credits include Multithreading for Visual Effects (2014), Intel® Xeon Phi™ Coprocessor High Performance Programming (2013), Structured Parallel Programming (2012), Intel® Threading Building Blocks: Outfitting C++ for Multicore Processor Parallelism (2007), and VTune™ Performance Analyzer Essentials (2005).

#### Time-Saving Tips as Spring Begins in the Northern Hemisphere

I love springtime. I carve out time so I can plant seeds to get our garden going. Nature gets busy, and everyday life seems to pick up as well. With so much to do, we all look for ways to make life easier, more efficient, and more productive. Software development can have its fair share of menial, time-consuming tasks. I definitely want to fast-forward past the tedious so there is more time for fun stuff.

In this issue, our authors offer some suggestions on how to provide less time-intensive ways to achieve better performance with some very specific solutions: AoS to SoA in C++, bi-endian compilation, and richer OpenMP\* support. It's fair to say that working to get vectorization can be tedious when reasoning which layout of data in memory will yield the best performance. Should AoS become SoA?

Our first feature, "**Improve Productivity and Boost C++ Performance**," discusses how the new Intel<sup>®</sup> SIMD Data Layout Template (SDLT) helps with memory layout optimization to potentially increase performance of SIMD-ready C++ code.

We do not make tools to settle Lilliputian disagreements about eggs, but we can help deal with compiling code for Intel® processors even if the code was written originally for big-endian processors. **"Intel® C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology**" describes how this edition of Intel® compilers can help easily migrate legacy applications from big-endian to little-endian architectures. Rather than extensively rewriting code, we can reuse code for both architectures with this helpful tool.

"OpenMP\* API Version 4.5: A Standard Evolves" is an in-depth look at the new version of OpenMP and how it helps us better express parallelism in applications and offloaded code. OpenMP 4.5 offers task-generating loops that relieve us from having to find solutions to tame load imbalances and resolve composability issues caused by parallel loops, among other benefits.

We may never escape life's seemingly endless to-do lists. But, we do offer some ways, in this issue, to save time in our pursuits of high performance for our applications. What you do with your time savings is up to you!

James Reinders March 2016

### IMPROVE PRODUCTIVITY AND BOOST C++ PERFORMANCE

Introducing the Intel<sup>®</sup> SIMD Data Layout Template (Intel<sup>®</sup> SDLT) to Boost Efficiency in Your Vectorized C++ Code

Udit Patidar, Product Marketing Engineer, Developer Products Division, Intel Corporation

Intel provides many tools to help you find hotspots in your code (e.g., Intel® VTune™ Amplifier XE) and offer advice on optimizing your code (e.g., Intel® Advisor XE). **Intel® C++ Compiler** generates detailed optimization reports that can tell you whether vectorization of a particular C++ loop was successful.<sup>1</sup> Intel is introducing a new template library included in Intel C++ Compiler, a component in Intel® Parallel Studio XE or Intel® System Studio. If you are an application developer using C++, you know it takes considerable effort to hand-optimize memory access layout. The **Intel® SIMD Data Layout Template** (Intel SDLT) library optimizes C++ codes by enabling the

programmer to switch from an array of structures (AOS) representation to a structure of arrays (SOA) representation with minimal effort or overhead. Such an SOA representation improves memory utilization and facilitates vectorization avoiding data-structure layout conversions.

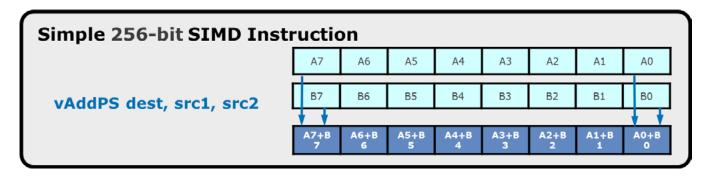

The latest Intel<sup>®</sup> processors and coprocessors offer vector instructions and support the single instruction/multiple data (SIMD) programming model. With Intel<sup>®</sup> Advanced Vector Extensions 512 (Intel<sup>®</sup> AVX-512) instructions, vectorized codes theoretically become capable of delivering 8x more peak performance for double-precision (or 16x single-precision) floating-point computations over the performance of nonvectorized codes. Unfortunately, the theoretical limit is rarely reached, especially on legacy codes that were not written with **vectorization** in mind. Without addressing the memory layout of data, you may end up leaving a lot of performance on the table.

In C++, the choice of how to lay data out in memory is crucial to achieving efficient vectorization. This is especially true when dealing with structures and arrays. It is common for developers to represent an array with a container from the C++ Standard Template Library, like std::vector.<sup>2</sup>

Although such a data layout might feel natural for a C++ programmer, the overhead of loading this AOS data set into vector registers can negate the performance gains of vectorizing. Converting the AOS representation to an SOA representation might be better suited for vectorization, but is very counterintuitive to the C++ programmer.<sup>3</sup>

Enter Intel SDLT.

The SDLT library provides an AOS interface to the user but stores the data in SOA format in memory. It abstracts the problem of **SIMD**-friendly data layout away from the programmer. Intel<sup>®</sup> SDLT offers a high-level interface using standard ISO C++11 features and does not require special compiler support to work. Because of its SIMD-friendly layout, it can better take advantage of the Intel<sup>®</sup> compiler's performance features such as OpenMP\* SIMD extensions and Intel<sup>®</sup> Cilk<sup>™</sup> Plus SIMD extensions.

To use the library, you declare your data types as primitives, describing them to SDLT. Then you can use your primitives with generic SDLT containers (instead of std::vector). Use the container's data accessors instead of array pointers or iterators. When used with an explicit vector programming model, the accessors from Intel SDLT containers handle data transformation and let the compiler generate efficient SIMD code.

When an accessor is used with the loop's index to export to or import from a local variable (inside loop body), the compiler's vectorizor can transparently access the underlying SIMD-friendly data format and, when possible, perform unit stride loads. In many cases, the compiler can optimize its private representation of local objects inside loop to be SOA. In the example above, because the container's underlying memory layout is SOA as well as the compiler's private representation of local objects, the compiler can generate efficient unit stride loads.

Representing data in memory SOA enables the compiler to directly load array elements into vector registers. This greatly helps SIMD vectorization reach its potential. In contrast, computing directly on AOS layouts can necessitate extra instructions to populate vector registers, essentially consuming execution slots but not contributing any results.

In summary, you can use SDLT to increase your productivity by letting it worry about optimal memory layout, as well as potentially increase performance of your SIMD-ready C++ code, as shown in the table below.

| Increase productivity<br>for developers using C++ | Rather than stop using C++ objects and revert to<br>C arrays when enabling SIMD code, use generic<br>containers with minimal effort. Let SDLT handle<br>data layout transformations for you.                          |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Improve performance                               | By making memory access contiguous, the<br>compiler can generate more efficient SIMD code<br>and, in some cases, utilize vectorization where<br>the overhead was previously too high.                                 |

| Integrate simply                                  | SDLT containers provide a similar interface to <b>std::vector</b> . Data accessors are compatible with existing Intel vector programming models and fit right in with other Intel <sup>®</sup> performance libraries. |

When evaluating whether SDLT might be suitable for you, consider this rule of thumb:<sup>4</sup> It is almost always better to vectorize than not to vectorize on Intel SIMD-capable hardware.

Given the increased number of data lanes in the latest Intel coprocessors, not carefully considering SDLT might prevent you from modernizing your code and exaggerate the shortcomings and downsides of traditional C++ applications. Try the new SDLT feature to enable an SOA layout for your C++ application. It might just improve your SIMD efficiency and give you a pleasant surprise.

#### SDLT Helps DreamWorks Animation Advance the State of the Art

The AOS-to-SOA problem is widely studied. And SDLT has already gained considerable traction in many industries. As an example, DreamWorks Animation has a mathematical library which was written using the standard C++ programming principles (i.e., without explicit vectorization in mind). It would be disruptive and difficult to manually change the data structure layout to an SOA on such a large scale. It was a large barrier to enabling SIMD, since the mathematical library affects almost all areas of character animation. Once refactored with SDLT, existing codes continued to compile (without changes) and loops could now be vectorized, showing great benefits.

"We used [SDLT] to vectorize the deformer code in Premo\*, the in-house animation tool for DreamWorks Animation. The performance improvements we were able to achieve were dramatic, and these improvements will translate directly into higher-quality characters that will be seen on-screen in future movies. Also, the library itself was easy to use and integrate into our existing codebase."

Martin Watt, DreamWorks Animation

#### Code samples and compiler documentation:

- 1. Averaging Filter implementation using Intel® SDLT

- 2. SDLT Code examples

- 3. More Intel SDLT code examples

#### References

- 1. "Get a Helping Hand from the Vectorization Advisor," The Parallel Universe Issue 23.

- 2. Introduction to the Intel<sup>®</sup> SIMD Data Layout Templates (Intel<sup>®</sup> SDLT).

- 3. How to Manipulate Data Structure to Optimize Memory Use on 32-Bit Intel® Architecture.

- 4. Case Study: Comparing Arrays of Structures and Structures of Arrays Data Layouts for a Compute-Intensive Loop.

### HOW TO GET THE INTEL® C++ COMPILER

Download a free 30-day evaluation of Intel® Parallel Studio XE > Download a free 30-day evaluation of Intel® System Studio > Find a reseller near you >

Students, educators, and open source contributors: Get a free copy >

# INTEL® C++ COMPILER STANDARD EDITION FOR EMBEDDED SYSTEMS WITH BI-ENDIAN TECHNOLOGY

Avoid Legacy Platform Lock-in from Big-E Platform and Software Dependencies and Easily Migrate to Little-Endian Architectures

Kittur Ganesh, Software Technical Consulting Engineer, Intel Corporation

**Intel® C++ Compiler** Standard Edition for Embedded Systems with Bi-Endian Technology is a productivity tool for developers locked into legacy platforms due to big-endian software dependencies who want to easily migrate their legacy applications from big-endian to littleendian architectures. Rather than rewrite the entire application code base, developers can speed migration with reduced code changes, code reuse, and one code base for both big-endian and little-endian architectures. The Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology also offers the performance benefits of the Intel<sup>®</sup> C++ Compiler, delivering outstanding application performance.

This article presents a comprehensive overview of the key features including the top issues to watch for when porting legacy applications to little-endian architecture systems.

#### Overview

In the early to mid-1990s, big-endian RISC architectures (e.g., SPARC\*, MIPS\*, PowerPC\*) dominated the embedded market segment and were used widely in computer networking, telecommunications, set-top boxes, DSL, cable modems, etc. In fact, most applications were developed for these systems. However, with the release of several new generations of faster, more scalable versions of x86 architecture processors, many developers faced a dilemma on how best to port these applications to the little-endian x86 architecture systems.

Although the applications are developed in standardized high-level languages (C/C++), traditional compilers can compile only to a single-endian architecture. Porting from one endian architecture to another becomes problematic if there are endianness byte-order dependencies in the source code bases, since it can result in severe runtime issues when executed on the target architecture. To address these dependencies, developers have to locate the hard-to-find, byte-order-dependent code and manually convert it to endian-neutral code—or satisfy the endianness of the target architecture.

If performance is a higher priority than time to market (TTM), migration through manual conversion can be very error-prone and expensive. If the application is already endian-neutral, it may just be a matter of recompiling the application, such as the EEMBC\* benchmark samples, which are endian-agnostic.

For applications that contain endianness dependencies, using the **Intel C++ Compiler** Standard Edition for Embedded Systems with Bi-Endian Technology can result in correct code generation while maintaining higher performance. In addition, porting is all about handling data endian types such as function prototypes and variable declarations, while the manual porting process involves handling bit-field accesses and shift operations, etc., which is tedious.

Unlike the Intel C++ Compiler, the Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology enables developers to compile and build applications with the byte order semantics in the source code bases intact, as long as the intended endianness of the byte order of dependent data is specified using the language extensions, a part of the compiler usage model (described later in this article). The compiler inserts byte-swap instructions where

necessary on the designated byte-order-dependent code so that the native endian architecture data in memory is converted into the target endian architecture byte order semantics for proper runtime execution.

The Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology is a command-line, Linux\* hosted, Linux target, stand-alone compiler specifically designed to enable developers to migrate applications from big-endian to little-endian architectures.

Benefits include:

- Faster and easier migration. Enables faster migration to little-endian Intel® architecture.

- **Minimal code changes.** Instead of requiring a rewrite of the entire application code base, the compiler allows reuse of the big-endian code base with minimal code changes, reducing implementation and validation effort.

- **Common code base.** Allows maintaining one code base for both big-endian and little-endian architectures.

The Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology is similar to the Intel C/C+ Compiler for Linux\* and shares a common core of technology related to optimization and performance models. The key difference between the compilers is the bi-endian technology, which is supported only in the Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology.

Usage model key features are outlined in the subsequent sections of this article through easyto-understand code snippets, including some common issues to watch for during the porting process. Understanding these key features should help developers quickly get started with the Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology to seamlessly migrate legacy applications to Intel architecture.

#### A Solution for Byte Endianness and Byte-Order Basics

Byte endianness is the system architecture attribute specifying the representation of data layout in memory for multiple byte access. The little-endian variables are stored with the least significant byte in the lowest memory byte address location, while the big-endian variables are stored with the least significant byte in the highest memory byte address. In this context, the big-endian model means that both big-endian and the little-endian data are allowed in memory accordingly.

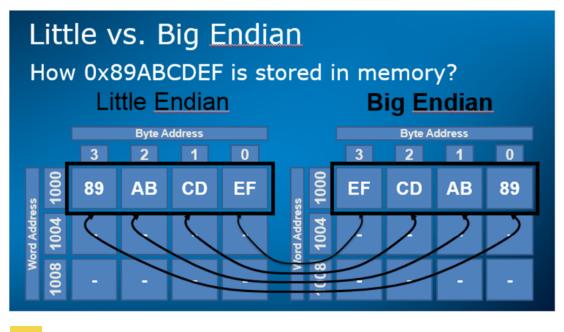

**Figure 1** shows the representation of the data 0x89ABCDEF in memory, with the big-endian variables using the opposite ordering of bytes within memory compared to little-endian variables, which have the least significant byte (EF) stored in the highest memory byte address.

1 Little vs. big-endian

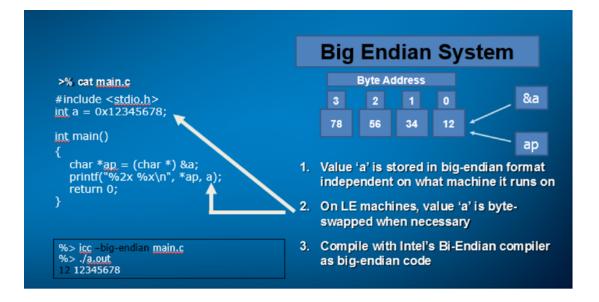

**Figure 2** shows a sample code snippet containing byte-order dependency, which produces different results when executed on big-endian versus little-endian architecture systems. As noted, on the little-endian system, the pointer ap points to 78, the least significant byte, while it points to 12 on a big-endian system. To fix this issue, the programmer can manually transform the byte-order code into endian-neutral code or reflect the endianness of the target architecture. But the manual process consumes enormous time and effort to identify byte-order-dependent code in legacy applications consisting of millions of lines of code—and can be error-prone as well.

**Figure 3** shows the Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology solution to the endianness dependency issue in **Figure 2**. The programmer needs to only identify the byte order of the data using the language construct (big-endian switch) for the compiler to enforce the big-endian byte order semantics—producing identical results on both architectures.

In the code snippet in **Figure 3**, value "a" is stored in big-endian format independent on which system the code is executed. On little-endian systems, the value "a" is byte-swapped by the compiler when necessary. The Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology inserts the byteswap (bswap) instruction to emulate the big-endian execution only when necessary, to minimize the generated instructions whenever possible to reduce performance overhead.

2 Byte-order-dependent code execution

3 Identical results on big-endian and little-endian systems

#### Usage Model and Language Support

The Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology provides bi-endian language extensions, enabling the developer to indicate the byte order (a type attribute) of data types including built-in types or typedef, code regions, and variable declarations. These language extensions enforce appropriate byte-order semantics on the assigned data types during execution on the target architecture.

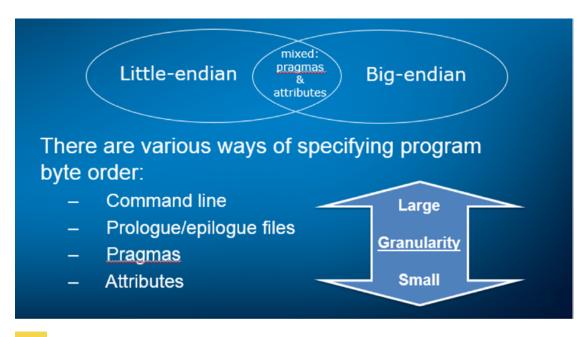

As shown in **Figure 4**, the Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology provides various ways of designating the program code byte order, such as command line switches, prolog/epilog files mechanism, pragmas, and attributes support.

The Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology resolves the data accesses using big-endian or little-endian conventions as supported through the implicit and explicit usage models. The implicit model is designed to designate the byte order for a file or an entire application through the use of command line options such as –big-endian or –little-endian switches or using the prolog and epilog files mechanism to set the implicit endian mode for the entire file or directories as well. It is advisable to use this implicit model where possible during the migration process for simplifying and accelerating the porting process.

The explicit model supports mixed-endian development through pragma byte-order attributes features. The programmer can designate the byte order of variables and functions at varying levels of granularity. The explicit model, due to this control on granularity levels, enables mixed-endian development.

4 Mixed-endian code development

**Figure 5** shows a a code snippet sample specifying endian byte order for directories using the prolog and epilog switches. Likewise, **Figure 6** shows a code sample using the command line switch –big-endian, #pragma byte\_order and attribute features at a finer granularity through explicit declarations. The command line option –big-endian sets the endian order for the whole program to big-endian byte order at a higher granularity. The #pragma byte\_order (push, little-endian) specifies that all the declarations following the # pragma are of little-endian byte order including any include files, except for the variable b, which is specified as big-endian through the endian attribute applied to a specific variable. Similarly, the developer can assign the byte order to different data types such as float, arrays, structures, and structures with bit-fields.

- Any directory ending with "/le" is little-endian (below)

-pe-udir-rule=".\*/le\$ /usr/include/le-prolog.h /usr/include/le-epilog.h"

- /proj1/ and /proj2/ directories are big-endian (below)

-pe-udir-rule="^/(proj1/|proj2/...) /usr/include/be-prolog.h /usr/include/be-epilog.h"

- Everything else is little-endian (below)

-pe-idir-rule="^/usr/include/le-prolog.h /usr/include/le-epilog.h"

- 5 Implicit mode using prolog and epilog feature

In general, the bi-endian functionality in the Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology can be summarized as follows: If the code is specified as bigendian, the compiler will treat the code as though it executes on the big-endian system and insert byte-swap instructions (bswap) at crucial points and, where possible, eliminate code to increase performance. Likewise, code specified as little-endian will run as native code, and the compiler will not insert any bswap instructions, since they are not necessary. The programmer can mix little-endian and big-endian code in the application.

**Figure 6** shows a code sample involving incompatible endian data type (msg) mismatch. To fix this issue, the user can use the –symcheck option, which then invokes the *bepostld* tool to perform a type match of all symbols used in the application. If it detects a type mismatch, it prints an error message with detailed information useful for the developer to fix the error. The *bepostld* tool is the bi-endian post link utility. It enables the programmer to identify incompatible type definitions for global variables and functions, in addition to performing the initialization of static big-endian pointers.

```

%cat main.c

#include <stdio.h>

#pragma byte_order (littleendian)

int a = 0x12345678;

int __attribute__((bigendian)) b = 0x12345678;

int main()

{

char* ap = (char*)&a;

char* bp = (char*)&b;

printf("%2x %x\n", *ap, a);

printf("%2x %x\n", *bp, b);

return 0;

}

%> icc -big-endian main.c

%> ./a.out

78 12345678

12 12345678

```

6 Byte order attribute usage at a finer granularity

#### Adopting Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology

As mentioned earlier, the 1990s saw many applications for big-endian architectures like SPARC, MIPS, and PowerPC. Many of these legacy applications are still used as part of the mixed-endian development environment. Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology can help accelerate the porting of old legacy code to Intel architecture systems.

Figure 7 shows a typical use case in such an embedded environment.

#### **Embedded Operating System**

- System library and GNU\* Libc (little-endian)

- HW interface (little-endian)

- Routing code in the user space (big-endian)

- Bi-Endian Interface (Linux\* OS and Libc)

- o System/libc calls are through an abstraction layer

- o Wrapper for used Libc and system service calls (customized)

#### Bare metal

- Own operating system and routing code (big-endian)

- HW Interface (little-endian)

- Bi-Endian interface is through the HW interface

Typical usage example

#### Top Issues to Watch For

Porting large legacy applications can be easier if the endianness of the directories is set correctly, eliminating all warnings on byte-order mismatch reported by the compiler, getting rid of endianness consistency errors reported by the **bepostld** tool across modules, and ensuring correct implementation of the function prototypes. Common issues during the migration process include:

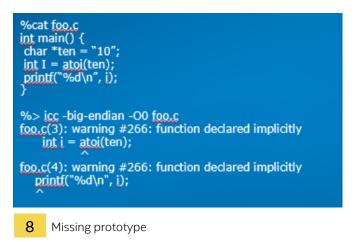

1. Missing prototype. Figure 8 shows an example. When the sample is executed, the program will crash, since the compiler has no indication that atoi() and printf() are little-endian and therefore incorrectly passes byte-swapped arguments. **Solution:** Add stdio.h and stdlib.h include files.

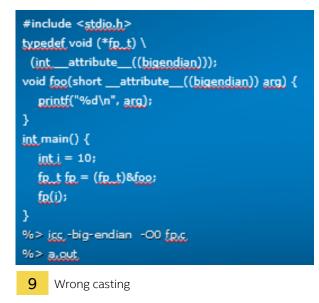

2. Wrong casting. Figure 9 shows a sample code snippet where the formal and actual arguments have different sizes. Solution: Compile with –param-byte-order=little-endian.

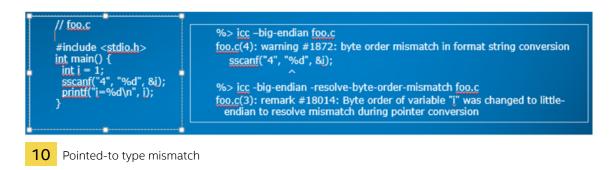

**3.** Pointed-to type mismatch. Figure 10 shows type mismatch as sscanf() assigns little-endian value in big-endian var 'i'. **Solution:** Declare 'i' as little-endian; swap value inside a wrapper for 'sscanf'. Or compile with –resolve-byte-order-mismatch to let the compiler fix the problem automatically.

**4. Missing byte order on the pointer type. Figure 11** shows a sample code snippet involving missing byte order on the pointer. The solution is to assign the correct endianness of little endian to the "end" pointer using the attribute feature as shown in **Figure 11**.

| // <u>foo.c</u>                                                                | %> icc –big-endian foo.c                                     |

|--------------------------------------------------------------------------------|--------------------------------------------------------------|

| #include < <u>stdlib.h</u> >                                                   | foo.c(11): warning #1696: implicit pointer conversion change |

| #include < <u>stdio.h</u> >                                                    | byte order                                                   |

| int main()                                                                     | d = strtod(str, &end);                                       |

| {                                                                              | ٨                                                            |

| char * <u>str</u> = "1.0 2.0";                                                 | Rectify as follows:                                          |

| char *end;                                                                     | char *endattribute((littleendian));                          |

| double d;                                                                      | ./a.out will produce:                                        |

|                                                                                |                                                              |

|                                                                                | 1.000000 2.0                                                 |

| d = <u>strtod(str</u> , &end);<br>printf("%lf \"%s\"\n", d, end);<br>return 0: | 1.000000 " 2.0"                                              |

**11** Missing byte order on pointer type

5. Variable length arguments. Figure 12 shows a code snippet involving variable length arguments. vprintf() retrieves vargs in little-endian byte order, but 'foo' is called with bigendian args, resulting in byte-order mismatch. Note that the compiler doesn't automatically adjust the byte order of arguments passed via va\_list. Also, the variable length arguments should be passed and retrieved in the same byte order (Figure 13).

**13** Variable-length args (continued)

- 6. main(). A few key points to note regarding the main() function arguments and byte order:

- Arguments to main are treated as little-endian by default:

```

typedef __attribute__((littleendian)) int leint;

int main( leint argc, char attribute ((littleendian)) **argv ) { }

```

• If big-endian arguments are required:

```

typedef __attribute__((bigendian)) int beint;

typedef __attribute__((bigendian)) char *pIntel C++ Compiler Standard

Edition for Embedded Systems with Bi-Endian Technologyhar;

int main (beint argc, pIntel C++ Compiler Standard Edition for Embedded

Systems with Bi-Endian Technologyhar *argv attribute ((bigendian)) {}

```

Note: Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology will not diagnose or warn for the above, as big-endian type is explicitly set in the code.

#### 7. Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology porting tips:

- Ensure correct endianness of files and directories.

- Eliminate all warnings on byte-order mismatch.

- Get rid of the errors reported by the **bepostld** utility.

- Watch out for big-endian issues caused by size mismatch (16 versus 32), variable arguments, function pointers, type casting, etc.

- Ensure correct function prototypes with proper endianness byte order.

#### Conclusion

Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology is a productivity tool for developers looking to overcome platform lock-in due to big endian software dependencies and migrate large legacy applications to little-endian architectures. We discussed some top issues to watch for when porting byte-order-dependent applications from big-endian to little-endian architectures. Also, the Intel C++ Compiler Standard Edition for Embedded Systems with Bi-Endian Technology shares a common core of technology related to optimization and performance models with the classic Intel C/C+ Compiler for Linux—delivering outstanding performance.

TRY THE INTEL<sup>®</sup> C++ COMPILER STANDARD EDITION FOR EMBEDDED SYSTEMS WITH B-ENDIAN TECHNOLOGY Learn more >

# **OPENMP\* API VERSION 4.5: A STANDARD EVOLVES**

Support for Heterogenous Programming with Easier Parallel Execution of Loops

Michael Klemm, *Senior Application Engineer*, Intel Corporation and Christian Terboven, *HPC Group*, RWTH Aachen University

The OpenMP\* API specification is a well-known and widely used standard for multithreading on shared-memory systems. Version 4.5 is the next step in the standard's evolution, introducing new concepts for parallel programming as well as additional features for offload programming.

#### History

The previous version of the OpenMP API specification (4.0) was released in July 2013. A major feature added was basic support for heterogeneous programming by offloading computation from the host to coprocessors. Due to the growing demand of the high-performance computing community for compute power, coprocessing gained a lot of interest. It became clear that OpenMP 4.0 lacked critical features to support heterogeneous programming optimally. At the same time, programmers are always required to look for new parallelization opportunities and to better express parallelism in their codes.

OpenMP 4.5 strives to improve offloading to coprocessors, as well as to add useful features to make **parallel programming** easier. In this article, we will describe three key new features of OpenMP 4.5:

- Task-generating loops for easier parallel execution of loops

- Locks with hints to expose more parallelism when using locks

- Improvements to offloading to make use of coprocessors in the system

A German version of this article was published in the online magazine Heise Developer.

#### Task-Generating Loops

Parallel loops are one of the most important parts of OpenMP applications. The traditional worksharing constructs (for in C/C++ and do in Fortran) are very simple ways of expressing thread-parallel loops by dividing loop iterations into chunks and distributing them across the threads in a parallel team. However, these constructs have several restrictions that complicate the life of a parallel programmer when dealing with large application codes. One of the most problematic issues is that nesting worksharing constructs in other worksharing constructs is prohibited by OpenMP. Because of that, one cannot nest a parallel loop inside another without creating a new team of threads to execute the inner parallel loop.

```

void taskloop_example() {

#pragma omp taskgroup

{

#pragma omp task

long_running_task() // can execute concurrently

#pragma omp taskloop collapse(2) grainsize(500) nogroup

for (int i = 0; i < N; i++)

for (int j = 0; j < M; j++)

loop_body();

}

}</pre>

```

Example code using the new taskloop construct with an OpenMP\* task

The new taskloop construct solves the problem by using OpenMP tasks to execute the loop chunks instead of assigning them directly to worker threads. Since OpenMP tasks can be nested arbitrarily, none of the nesting restrictions of worksharing constructs apply. Figure 1 shows how to mix OpenMP tasks and the taskloop construct. The OpenMP task in the example calls the function long running task() to mimic some long-running activity that can execute concurrently with the following loop. The taskloop construct then cuts the loop's iteration space into chunks and creates one OpenMP task for each chunk. Any free worker thread picks up one of these tasks and executes it. If the long-running task finishes early, its executing thread can also pick up tasks created by the taskloop. Because tasks may be nested arbitrarily, each of the executing tasks may, in turn, create new ones to further increase the level of concurrency in the application. The OpenMP runtime system takes care of load balancing the tasks across workers until all tasks have been executed.

```

template<class K, class V>

struct hash_map {

hash_map() {

omp_init_lock(&lock);

~hash map() {

omp_destroy_lock(&lock);

V& find(const K& key) const {

V* ret = 0;

omp_set_lock(lock);

ret = internal_find(key);

omp_unset_lock(lock);

return *ret;

void insert(const K& key, const V& value) {

omp_set_lock(lock);

internal_insert(key, value);

omp_unset_lock(lock);

}

//...

private:

mutable omp_lock_t lock;

hash_buckets *buckets;

// ...

};

```

```

2 Example of a hash map to map keys to values

```

The taskloop construct inherits its syntax from both the worksharing constructs and the tasking constructs. Besides the usual clauses to control visibility and sharing of data (shared, private, firstprivate, and lastprivate), it also supports the task clauses (final and mergeable). In addition, the construct accepts the nogroup clause that deactivates the implicit task group that automatically synchronizes all tasks created by the construct. In the example, we use an explicit taskgroup construct to synchronize execution of the long-running task and the taskloop construct.

The size of the generated tasks can be controlled by the grainsize clause. It defines how many loop iterations are assigned to each created task. If the programmer prefers to specify the number of tasks, the num\_tasks clause can be used instead. Finally, collapse can be used to create a product loop out of perfectly nested loops. This is similar to what the collapse clause achieves for worksharing constructs.

OpenMP 4.5 also extends the OpenMP task constructs task and taskloop with the priority clause. It can be used to influence the order of task execution by the runtime system. The clause takes a positive integer value: the higher the value, the higher the priority of the created task. It is used as a hint to the runtime system to suggest that it should execute tasks with higher priority before tasks with lower priority. However, the OpenMP implementation is not required to adhere to the hint, so one cannot assume that using priorities guarantees a certain ordering of task execution. If the programmer does not specify any priority, it is assumed to be zero by default.

#### Locks, Locks, Locks

Mutual exclusion by acquiring and releasing locks is an inevitable evil in many parallel programs. To avoid race conditions and data corruption, locks usually have to be taken before entering a code region that accesses a shared resource. This protection of the resource comes with a price to pay in terms of serializing execution and thus limiting parallelism. In some applications, locks are placed for safety reasons, despite the fact that the probability of a conflict due to concurrent access to the shared resource is very low, but not zero.

The example code in **Figure 2** shows a very simplistic and inefficient implementation of a hash map used to map a key of type **K** to a value of type **V**. Despite being a short example without error handling or other optimizations, the code shows one particular locking issue. The mutual exclusion is activated by acquiring the lock immediately after entering each of the methods of the **hash\_map** class. The effect is that execution is serialized to avoid potential

```

template<class K, class V>

struct hash map {

hash map() {

omp_init_lock_with_hint(&lock,

kmp_lock_hint_hle);

}

~hash map() {

omp_destroy_lock(&lock);

3

V& find(const K& key) const {

V* ret = 0;

omp_set_lock(lock);

ret = internal_find(key);

omp unset lock(lock);

return *ret;

3

void insert(const K& key, const V& value) {

omp_set_lock(lock);

internal insert(key, value);

omp unset lock(lock);

}

private:

mutable omp_lock_t lock;

hash buckets *buckets;

};

```

3 Using speculative locks to optimistically execute a critical region

race conditions on the individual hash buckets. However, this is frequently unnecessary, as data structures with hash functions are designed to avoid access conflicts as much as possible. It would thus be perfectly safe for multiple threads to enter the hash map code if each thread works on a different hash bucket or element. In typical implementations you will find locks to protect individual buckets or elements, or even lock-free data structures. In any case, getting to a scalable and efficient solution requires a lot of engineering work.

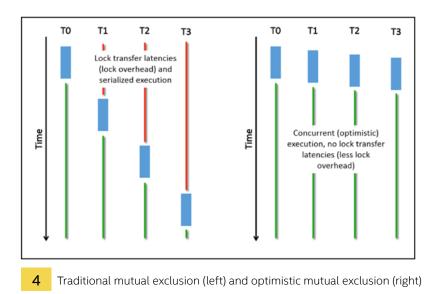

OpenMP 4.5 offers a new feature to alleviate this burden. Programmers can use a new API to pass a hint for each lock to the OpenMP runtime and inform it about the intended usage of the locks in the application code. Two new functions to initialize a lock are defined: omp\_init\_lock\_with\_hint and omp\_init\_nest\_lock\_with\_hint. These functions accept an additional argument of type omp\_lock\_hint\_t (see Table 1 for possible lock hints). As with other hints in OpenMP, the implementation can use the hint to optimize the lock implementation for the intended usage. For instance, the implementation can then replace a test-and-set lock with a lock based on futexes (short for "fast userspace mutex"). Or it can make use of special hardware instructions, e.g., Intel® Transaction Synchronization Extensions (Intel® TSX). In all circumstances, the lock semantics are preserved so that the observable behavior of the program is not affected.

The hints are integer expression, so that they can be combined by the | operator in C/C++ or by the + operator in Fortran. This gives a programmer more flexibility in expressing the desired usage of a particular lock. The OpenMP standard also explicitly allows an implementation to extend the predefined hints with additional hints. The Intel OpenMP runtime makes use of this by defining the additional hints listed in **Table 2**.

| Hint                         | Semantics                                                                                                             |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| omp_lock_hint_none           | The OpenMP runtime can freely choose the lock implementation.                                                         |

| omp_lock_hint_uncontended    | Threads rarely access the lock concurrently, so expected contention is low.                                           |

| omp_lock_hint_contended      | Optimize the lock for frequent conflicts by multiple threads trying to acquire the lock at the same time.             |

| omp_lock_hint_nonspeculative | Do not use optimistic locking; there are too many conflicts due to overlapping working sets of the acquiring threads. |

| omp_lock_hint_speculative    | Use optimistic locking; the working set of the threads is expected to be distinct so that conflicts are unlikely.     |

Table 1. Supported lock hints in OpenMP\* 4.5

| Hint                   | Semantics                                                                                                                                    |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| kmp_lock_hint_hle      | Use hardware lock elision feature of Intel® TSX for the lock.                                                                                |

| kmp_lock_hint_rtm      | Use a lock implemented with the restricted transactional memory feature of Intel® TSX.                                                       |

| kmp_lock_hint_adaptive | Use a speculative, adaptive lock that checks for contention and falls back to a traditional test-and-set lock in case of too many conflicts. |

Table 2. Additional lock hints as defined by the Intel® OpenMP\* runtime

In **Figure 3**, the code uses the new feature to pass information to the OpenMP runtime that the lock should be executed speculatively, as the programmer assumes that thread will not conflict while accessing the hash map. On a processor with Intel TSX, the hardware will optimistically ignore the lock instead of acquiring and releasing the lock (see **Figure 4**). Only if the hardware detects that lock semantics have been violated—for instance, if one thread modified a hash bucket while another thread was reading from it—will the processor revert and re-execute code with traditional locking for mutual exclusion.

As a rough guideline for when to use speculative locking, one can consider two fundamental cases. First, Intel TSX and speculative locking pay off if a lock is uncontended and does not produce a lot of conflicts (as in the hash table example). Second, if many readers but only a few writers compete for a lock and thus produce a lot of contention, but almost no conflicts, then a speculative lock can reduce the lock overhead as well.

#### Offloading

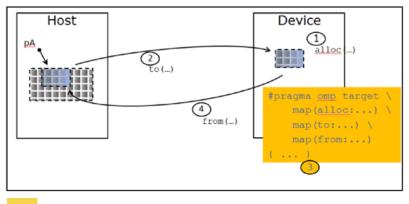

OpenMP 4.0 extended the multithreading paradigm of OpenMP with heterogeneous offloading to attached compute devices such as coprocessors. The target construct sends the control flow from a host thread to the coprocessor. Programmers can use the map clause to specify data objects to be transferred and the direction of the data transfer (see **Figure 5**). Usually, the offloaded code regions are known as kernels and are massively parallel fragments that make use of the respective properties of the target device.

5 Execution model for offloaded code regions including data transfers

OpenMP 4.0 introduced device data environments that can keep data alive across different offload regions to save expensive data transfers between the host and target. **Figure 6** shows an example of such a data region that keeps **var1** on the target device during the invocation of **kernel1** and **kernel2**. The duration of the data region is bound to the lexical scope structured block associated with the **target data** construct. When the code reaches the opening curly brace, the data environment is created and data is transferred. Once the code reaches the closing curly brace, the data environment is destroyed. While this allows the implementation to keep the environment across multiple kernel invocations, it prohibits the mapping of new data or the mapping of data in an unstructured way, e.g., in the constructor or destructor of the C++ class.

```

double var1[N];

void offload_example() {

#pragma omp target data map(tofrom:var1[:N])

{

C *c = new C();

#pragma omp target

c.kernel1(); // uses var1 and members of C

#pragma omp target

c.kernel2(); // uses var1 and members of C

delete c;

}

}

```

6 Device data environments bound to the lexical scope of the target data construct

OpenMP 4.5 provides new constructs to overcome these restrictions. The target enter data and target exit data directives create and destroy data mapping on the target device:

```

#pragma omp target enter data map(map-type: var-list) [clauses]

#pragma omp target exit data map(map-type: var-list) [clauses]

```

**Figure 7** shows how the new directives can be used to create and destroy data environments in a C++ object's constructor and destructor. When an instance of the C class is constructed, the values member is mapped to the target device. When the object is destroyed, the destructor also disposes of the data environment associated with values.

Another extension concerns the mapping of elements of structured data types. OpenMP 4.0 allowed only scalar variables, arrays, or bitwise copyable data structures to be mapped. OpenMP 4.5 extends data transfers to cover partial mapping of members of structured data types. **Figure 8** shows a few of the new possibilities.

Finally, OpenMP 4.5 contains support for asynchronous offloading. Previously the host thread waited for the completion of the offloaded code region before it continued with execution. With the **nowait** clause, programmers can turn a **target** construct into an OpenMP task that is executed concurrently with the encountering host thread. The **target enter data** and **target exit data** directives also support the new clause to allow for asynchronous data transfers.

Because the asynchronous offloads and data transfers are regular OpenMP tasks, the new feature inherits the **depend** clause to synchronize asynchronous execution with other OpenMP tasks executing on the host. The example code in **Figure 9** performs an asynchronous

```

class C {

public:

C() {

#pragma omp target enter data map(alloc:values[M])

}

~C() {

#pragma omp target exit data map(delete:values[M])

}

private:

double *values;

};

```

Creating and destroying device data environments in C++ objects

```

struct A {

int field;

double array [N];

} a;

#pragma omp target map(a.field)

#pragma omp target map(a.array[23:42])

```

7

Mapping of elements in structured data types

9

Asynchronous offloading and data transfers and synchronization with host threads

data transfer that overlaps with host execution. The **depend** clause defers the kernel invocation until the data transfer has completed. The same kind of dependency avoids premature data transfer back from the device, unless kernel execution has finished. Finally, the host thread creates a task that is awaiting completion of the last data transfer, before it starts concurrently to execute the host code in **do\_something\_on\_the\_host\_3()**.

#### Conclusion

Besides several corrections, OpenMP 4.5 brings new features that enable programmers to better express parallelism and to increase the performance of both host applications and offloaded code. Task-generating loops relieve programmers from cumbersome solutions to tame load imbalances and resolve composability issues caused by parallel loops. Support for locks with hints provides an easy way for programmers to optimize the locking behavior of their applications and to exploit modern processor support for hardware transactional memory in a portable manner. Finally, the extensions to offloading allow for asynchronous execution to overlap computation and communication on both the host and the attached coprocessors.

### NEED AN OPENMP-COMPATIBLE COMPILER? TRY INTEL® C++ OR FORTRAN COMPILERS.

Part of Intel<sup>®</sup> Parallel Studio XE and Intel<sup>®</sup> System Studio >

### INTEL® MPI LIBRARY: SUPPORTING The hadoop\* ecosystem

#### MPI Often Outperforms Hadoop MapReduce in Tasks with Heavy Computations

Mikhail Smorkalov, Software Development Engineer, Intel Corporation

For decades, **MPI** has dominated as the model to use in distributed calculations. However, with high-performance computing (HPC) incorporating workloads requiring processing of huge volumes of input data, new approaches and frameworks have appeared. The most popular ones are the Apache Hadoop\* MapReduce paradigm<sup>1</sup> in general and the Hadoop software stack (including all tools and frameworks running on top of it) in particular.

Vanilla Hadoop is composed of several modules<sup>2</sup> and implies certain constraints on the scope of problems it can solve efficiently. For example, MapReduce is not good at iterative algorithms since it requires dumping the intermediate results to the storage between the iterations. These

shortcomings triggered development of other frameworks on top of Hadoop, e.g., Apache Spark\*, Apache Storm\*, which allow for efficient in-memory data caching between the iterations. Moreover, YARN\*, as a cluster management framework, allows for arbitrary paradigms, not only MapReduce, thus broadening the area of Hadoop applicability to the fields where mostly MPI could be found previously.

While some tasks can be solved much more easily and efficiently using the Hadoop stack, even machine learning that often requires a lot of heavy computations and intensive internode communication gains popularity on the Hadoop platform—although multiple studies<sup>3,4</sup> demonstrate that MPI outperforms Hadoop frameworks significantly in this sphere. With some, there is a misconception that MPI is just for HPC. This article helps shed some light on benefits and challenges connected with using MPI in the Hadoop ecosystem, complementing or supplementing the tools commonly used in this area.

#### **New HPC Challenges**

Historically, high-performance computations dealt with compute-intensive areas, like weather modeling, physics, and chemistry, where input is relatively small but the number of calculations— and sometimes the volume of output data—is huge. MPI is the best fit for such problems, providing a number of communication patterns, and usually MPI implementations, that use hardware capabilities in a highly efficient way.

However, new application domains require creation of data-intensive applications that operate on terabyte and petabytes of input data. Frequently, they do not require a lot of internode communication, so efficient, reliable, and scalable input/output (IO), becomes a very significant aspect. This aspect is addressed by HDFS\* in Hadoop.

Another challenge is that the duration of data analytics tasks can be quite significant—making transparent fault management a must. Moreover, streaming tasks may run permanently, so a node crash is inevitable at some point. The Hadoop software stack encapsulates a mechanism for graceful task handover without the need to restart the whole job. Only failed subtasks are handed over to healthy nodes. Also, the Hadoop scheduler does its best to run tasks as close to data as possible, thus securing the best possible data locality.

All these features make the Hadoop platform attractive for data scientists and analysts. And this has stimulated development of multiple analytics frameworks and libraries in the Hadoop ecosystem. These frameworks allow for using many programming languages (e.g., Python\*, Java\*, Scala\*), thus lowering barriers to entry. MPI implementations traditionally provide only C and Fortran bindings required by the standard. It is worth mentioning that some MPI implementations provide Java and Python interfaces.

#### **MPI Repertoire**

First, let's consider the rich and comprehensive set of MPI communication patterns that can be used to implement the MapReduce program. Obviously, the Map phase can be implemented via MPI\_Scatter(v) functions, while the natural choice for the Reduce phase is either MPI\_Reduce<sup>5</sup> or, if the reduction needs all data in place to proceed, MPI\_Alltoall(v), followed by some merge operation. Moreover, the MPI implementations usually provide several algorithms for each collective operation and select the optimal one depending on the scale, message size, and hardware architecture. So the main operations used in the Hadoop world have natural analogs in MPI. But what about fault management and data management functionalities, which are vital for the big data world? Does MPI provide something to address those challenges?

Indeed, Hadoop scalability is great due to the data locality aspect that means getting data from the storage closest to the process whenever possible. The HPC world uses parallel file systems accessed via network, thus putting serious requirements on the network bandwidth and load balancing when working with huge input data. However, modern parallel file systems (e.g., Lustre\* or GPFS\*) are supposed to provide near-linear scalability with increasing the system size. This means they can be used for scalable data management. Moreover, Intel's distribution of Lustre takes care of running Hadoop over the Lustre file system with optimal data access.<sup>6</sup> While it is not always possible to keep absolute data locality when running Hadoop applications, parallel file systems can provide applications with fast parallel access to remote data.

Even in the Hadoop world, people tend to file systems different from HDFS.<sup>7,8</sup> The advantages come from the parallel nature of those storage systems and high-bandwidth interconnects that are used in HPC clusters. For example,<sup>8</sup> shows that Lustre FS\* can provide much faster data access than even local drive access on commodity nodes.

Moreover, MPI-IO includes collective IO operations that can be tuned flexibly. For example, they allow for collective buffering so that the only process on the node is writing/reading to the FS, thus decreasing concurrency when doing IO.

As for fault tolerance, it is definitely one of the strongest advantages of the Hadoop platform. It allows for almost transparent recovery in case of hardware failure. At the same time, fault tolerance is a rather weak side of the MPI standard. Some implementations may allow for writing fault-tolerant MPI programs by following special workflow,<sup>9</sup> but it requires significant efforts from application engineers. User-level fault tolerance that may be introduced in the MPI 4.0 standard also does not introduce any transparent fault management, but at least should make the life of MPI developers easier. The only transparent fault management mechanism available in MPI is check-pointing.<sup>10</sup> It is based on global snapshots, though, implying that absolutely all tasks (even healthy ones) will be restarted from the checkpoint. So, this is one of the few aspects where MPI implementations are obviously inferior to Hadoop—making MPI less than optimal for long-running services such as streaming processing apps.

Another advantage of the Hadoop ecosystem is the wide community that contributes to the Hadoop ecosystem in different areas. A number of tools and technologies provide convenient access to different types of data sources such as files, relational databases, and streams. On the other hand, MPI is a relatively low-level technology focused on performance, so it does not provide a lot of syntax sugar in API. However, initiatives like Intel® Data Analytics Acceleration Library (Intel® DAAL)<sup>11</sup> introduce a way to efficiently implement the whole dataflow, from reading data from different data sources to transformations and calculations on them, including a broad range of algorithms. This may attract developers who previously did not want to bother with implementing all dataflow by themselves but would like to get the performance advantages of MPI.

Also, it is worth mentioning that vanilla Hadoop uses TCP/IP for communication between the nodes in the shuffling phase, making getting benefits from fast interconnects complicated. There are initiatives related to using RDMA for intercommunication,<sup>12</sup> though.

Finally, many people consider the high scalability of Hadoop when selecting the tools for solving their task, but MPI is generally also very good in this. For example, **Intel® MPI Library**'s proven scalability is up to 340,000 processes.<sup>13</sup>

#### Running MPI in the Hadoop Ecosystem

As the previous sections show, MPI can address some of the challenges of emerging HPC, being a competitor to Apache Spark in certain areas. However, using MPI with Hadoop tools and frameworks is complicated, since HPC and Hadoop used to progress in parallel, following the needs of most common applications in corresponding areas, thus utilizing different ecosystems, including resource managers. Current activities related to merging HPC and Hadoop worlds are mostly focused on moving Hadoop tools into the HPC environment (or even implementing new MapReduce frameworks atop MPI, such as MR-MPI<sup>14</sup>) to utilize performance advantages provided by high-end systems. However, while speeding up data analytics and machine learning applications by running them on HPC clusters is one of the options (and maybe the most promising one),<sup>15</sup> its value is not that obvious for companies that already have Hadoop infrastructure and successfully use it.

Another option is running MPI applications in the Hadoop environment without maintaining two different infrastructures on the cluster or setting up two different clusters.<sup>16</sup> This section describes the mechanism for integrating MPI into the Hadoop ecosystem built on top of Cloudera Distribution Including Apache Hadoop\* (CDH\*).<sup>17</sup>

The CDH package includes Llama<sup>\*,18</sup> an application master for YARN, originally designed to be used by Impala<sup>\*,19</sup> Llama provides a cross-language Apache Thrift<sup>\*</sup> API for requesting and releasing resources and some additional functionality (e.g., gang scheduling, which is vital for running MPI). With this set of features, it becomes possible to programmatically obtain information about Hadoop cluster nodes and request the resources for an MPI job when needed, and thus to share the same infrastructure dynamically between MPI and Hadoop jobs.

To make use of Llama functionality and gracefully run MPI on a Hadoop cluster, two complementary services need to be implemented:

- **MPI Llama client:** Entity that queries Llama to get required information (e.g., cluster node names) and request/release resources.

- **MPI Llama callback service:** Daemon that waits for notification from Llama on certain events (e.g., node allocation).

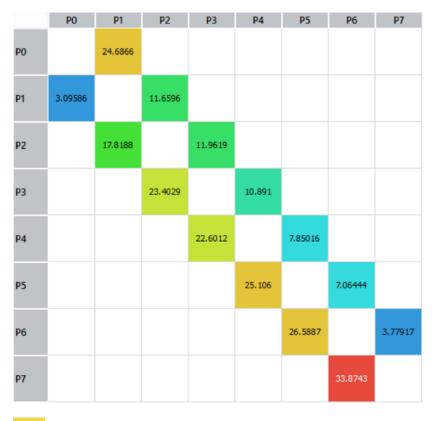

The actual workflow consists MPI of three independent phases mpiLlamaClient mpiCallbackService llamaAM runtime (Figure 1): Start calback service • Start-up: Launching Register mpiLlamaClient complementary services (client and callback service and callback), registering them in Llama, and requesting resources Start-up phase based on MPI job needs. This Request resources phase is finished as soon as the callback service gets notification Resources allocated that resources are allocated. -OK -Resources allocated-• MPI job start: Natively running the MPI job on Hadoop cluster Start MPI job on nodes, based on the resource list allocated nodes provided by Llama. Compute Start MPI job • Finalization phase: Releasing resources and shutting down -MPI job completedcomplementary services when the MPI job has finished. Release resources OK Finalization Unregister mpiLlamaClient stage and its callback service OK Exit mpiLlamaClient and callback service

1

Running MPI in a Hadoop\* cluster

One obvious advantage of this mechanism is that Llama communication time does not depend on the MPI application complexity, so it just adds constant overhead compared to a pure MPI run. This means that all results related to a performance comparison between MPI and Hadoop/Spark applications are still relevant, since the contribution of Llama communication overhead into the total wall time would be vanishingly small for real applications.

Another advantage of this approach over the others (e.g., the academic mpich2-yarn<sup>20</sup> project) is that it is not tied to a certain MPI implementation, since requesting resources and launching MPI jobs are independent phases of the workflow. Thus, moving to another MPI implementation is a matter of changing MPI launch command. For example, using BDMPI<sup>21</sup> as an MPI implementation provides a way to use MPI for efficient execution of out-of-core algorithms, making it a flexible alternative to native Hadoop frameworks for big data problems.

The functionality described above has been implemented in the Intel<sup>®</sup> MPI Library 5.1 Update 2 (please see the Intel MPI reference guide for an exact usage model).

It's also important to realize that running MPI on a Hadoop cluster generally imposes some limitations:

- MPI-IO is available on shared folders only or locally, as MPI implementations do not support HDFS. This means the cluster admin may want to set up an NFS folder in addition to HDFS.

- YARN does not provide information about container CPU affinity, so pinning functionality should be used carefully when more than one application is running on the same node.

## Performance Evaluation

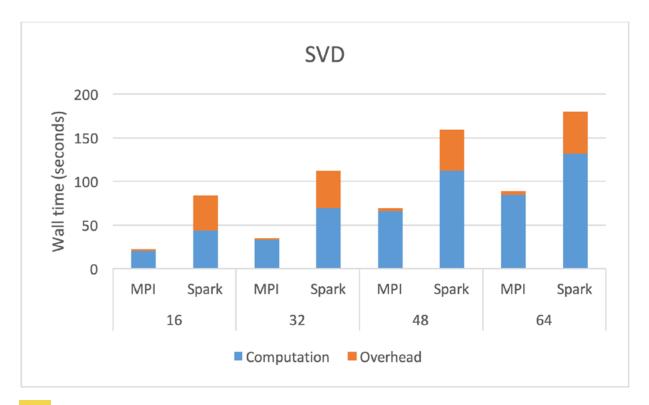

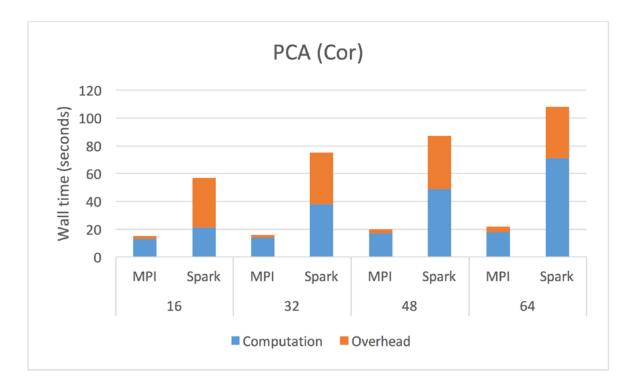

Two distributed algorithms commonly used in data analytics are selected as a target:

- 1. Singular value decomposition (SVD)

- 2. Principal component analysis (PCA, using the correlation method)

Spark- and MPI-backed samples for each of the algorithms are taken from the Intel DAAL distribution and composed of the same building blocks, so the performance difference is explained by different distribution frameworks (Spark versus MPI) and languages (Java versus C), but not by implementation details. The Spark-backed SVD sample has also been modified to avoid collecting the left orthogonal matrix on driver node as that is generally excessive and doesn't benefit from the Spark paradigm of RDDs (so the complexity of the Spark-backed algorithm is a bit lower than for the MPI-backed one).

In our performance studies, we used an eight-node cluster in which each node is equipped with one Intel® Xeon® processor X5570, one NetEffect\* NE020 10 Gb accelerated Ethernet adapter, and 12 GB of RAM. The cluster was running the SLES\* 11.0 Linux\* operating system and the Cloudera Express\* 5.4.6 version of CDH (Spark v.1.3.0). We used Intel MPI Library Version 5.1.2, Intel DAAL 2016 Update 1, Intel® C++ Compiler Version 15.0.4, JDK v.1.7.0\_67, and Scala v. 2.10.4.

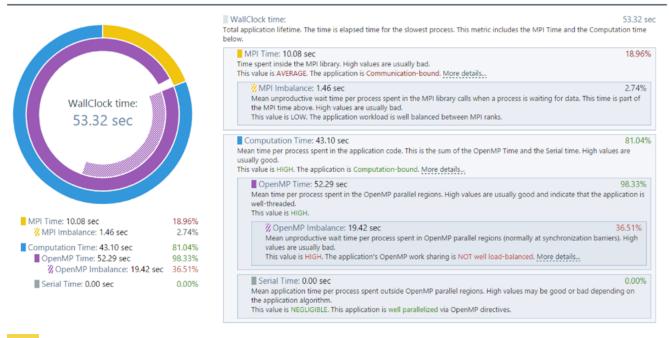

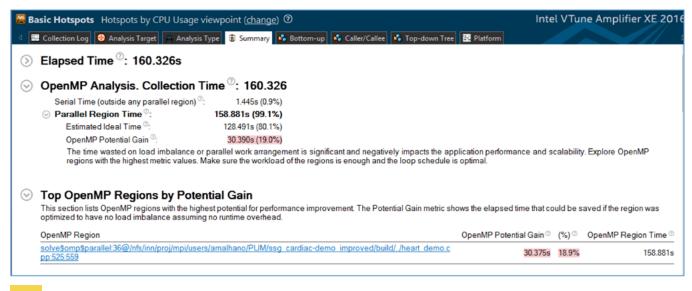

Performance was measured on 16, 32, 48, and 64 data blocks, each containing 10,000 x 1,000 elements of the input matrix. The full dataset of 64 blocks was 4.2 GB in size. When running the MPI-backed sample, one MPI process per block was started. For Spark, the desired number of executors was set to the number of blocks via the spark.executor.instances property, which is not always respected since Spark follows its own heuristics when it defines the number of executors. Also, since Spark is quite sensitive to JVM and its own configurations, memory settings were selected empirically (listed under **Figures 2** and **3**) to facilitate the best performance.

2 Singular value decomposition

spark.executor.memory = 1300m spark.yarn.executor.memoryOverhead = 1024m spark.kryoserializer.buffer.max.mb = 512m

3 Principal component analysis

spark.executor.memory = 1024m spark.yarn.executor.memoryOverhead = 768m

Total wall time in the measurements above consists of two summands—actual calculation and the overhead. The latter, for the MPI sample, is defined as the time required for Intel MPI to negotiate the resources with Llama and start the MPI job, and for Spark—as a difference between the wall time and sum of durations of all computation stages.

Note that since MPI is sensitive to running in oversubscription mode, performance may be a bit degraded when the number of MPI ranks is higher than the number of physical cores. However, the wall time is still much shorter than for Spark.

### **Conclusions and Outlook**

The measurements previously mentioned, together with other published results,<sup>3, 4</sup> demonstrate that MPI can be a good fit for some algorithms used in data analytics, and MPI integration into the Hadoop ecosystem proposed in this article allows for broader MPI usage in this area.

It is important to understand that although MPI can significantly outperform and replace Hadoopbased frameworks for some problems, it is not as well suited for others. So, it is more natural to use them together, providing a new level of synergy. Some long-running services may be implemented with Hadoop tools, while relatively short tasks, which involve a lot of computations and tricky communication, can be moved to MPI.

Besides the performance that MPI can provide, there are millions of lines of MPI code created over the years on which Hadoop developers can piggyback. Furthermore, with data analytics breaking into HPC world and emergence of the high-performance data analytics domain, the question of using MPI and big data frameworks in the same ecosystem should get more attention. Integration of MPI into the Hadoop ecosystem is one of the options to address it.

## **BLOG HIGHLIGHTS**

#### Three Pieces of Advice for Code Modernization Success

BY CLAY BRESHEARS >

I got an email request to write a blog about three things I would advocate to a programmer that could be used to speed up her program. My first flippant thought was, "Location! Location! Location!" That got me thinking about real estate and led my meandering mind to answer the original query with a paraphrase of Blake (played by Alec Baldwin) from the film *Glengarry Glen Ross*: "A-B-C. A-Always, B-Be, C-Concurrent. Always be concurrent."

I quickly realized such a simple quote was packed with so much more than just three simple things. I've written dozens of IDZ blog posts on individual items (granularity, load balance, task decomposition, parallelizing loops, etc.) that would be much more relevant. (If you can find them online, feel free to pick three and don't bother to finish reading the rest of this post. Or, better yet, finish reading this one now and search online later for more focused recommendations.) I even wrote a book on the topic of concurrent and parallel programming. If you've got a copy, take out any three pages from the latter half of the book and you'll likely have three different things you can do to speed up code. (Also, now that you've ruined your copy by tearing out those three pages, feel free to buy another copy.)

**Read more**

>

### References

- 1. J. Dean and S. Ghemawat. "MapReduce: Simplified Data Processing on Large Clusters." Comm. ACM, 51(1): 107–113, January 2008.

- 2. Apache Hadoop Wiki, hadoop.apache.org/#What+Is+Apache+Hadoop%3F.

- 3. S. Jha, J. Qiu, A. Luckow, P. Mantha, and G.C. Fox. "A Tale of Two Data-Intensive Paradigms: Applications, Abstractions, and Architectures," eprint arXiv:1403.1528, March 2014.

- 4. F. Liang, C. Feng, X. Lu, and Z. Xu. "Performance Benefits of DataMPI: A Case Study with BigDataBench." In *The 4th Workshop* on *Big Data Benchmarks, Performance Optimization, and Emerging Hardware*, BPOE-4, Salt Lake City, Utah, 2014.

- 5. T. Hoefler, A. Lumsdaine, and J. Dongarra. "Towards Efficient MapReduce Using MPI." Recent Advances in Parallel Virtual Machine and Message Passing Interface, pp. 240–249, 2009.

- "Intel® Enterprise Edition for Lustre\*," intel.com/content/www/us/en/software/intel-enterprise-edition-for-lustre-software.html.

- A. Woodie. "What Can GPFS on Hadoop Do For You?" Datanami, February 2014, datanami.com/2014/02/18/what\_can\_gpfs\_on\_hadoop\_do\_for\_you\_/.

- 8. N. Rutman. "Map/Reduce on Lustre: Hadoop Performance in HPC Environments" (technical white paper). Xyratex, xyratex.com/sites/default/files/Xyratex\_white\_paper\_MapReduce\_1-4.pdf.

- 9. W. Gropp and E. Lusk. "Fault Tolerance in MPI Programs." The International Journal of High Performance Computing Applications, Volume 18, No. 3, Fall 2004, pp. 363–372.

- 10. J. Hursey, J.M. Squyres, and A. Lumsdaine. "A Checkpoint and Restart Service Specification for Open MPI" (technical report), open-mpi.org/papers/iu-cs-tr635/iu-cs-tr635.pdf.

- 11. "Announcing Intel<sup>®</sup> Data Analytics Acceleration Library 2016 Beta," software.intel.com/en-us/articles/announcing-intel-data-analytics-acceleration-library-2016-beta.

- 12. High-Performance Big Data Project, Network-Based Computing Laboratory, Ohio State University. "RDMA-Based Apache Hadoop," hibd.cse.ohio-state.edu.

- 13. Intel® MPI Library, software.intel.com/en-us/intel-mpi-library.

- 14. S. Plimpton. "MapReduce and MPI." SOS 17 Intersection of HPC & Big Data, March 2013.

- 15. J. Dursi. "HPC Is Dying, and MPI Is Killing It." dursi.ca/hpc-is-dying-and-mpi-is-killing-it.

- The Nielsen Company. "Bridging the Worlds of High Performance Computing and Big Data," sites.nielsen.com/newscenter/bridging-the-worlds-of-high-performance-computing-and-big-data.

- 17. "CDH Components," cloudera.com/content/cloudera/en/products-and-services/cdh.html.

- 18. Cloudera, Inc. "Llama," cloudera.github.io/llama.

- 19. Cloudera, Inc. "Apache Impala," impala.io.

- 20. GitHub, Inc. "mpich2-yarn," github.com/alibaba/mpich2-yarn.

- 21. Karypis Lab. "BDMPI Big Data Message Passing Interface," glaros.dtc.umn.edu/gkhome/bdmpi/overview.

## TRY INTEL<sup>®</sup> MPI LIBRARY

A part of Intel<sup>®</sup> Parallel Studio XE Cluster Edition >

## FINDING YOUR MEMORY ACCESS PERFORMANCE BOTTLENECKS

Improve Application Performance Quickly and Simply with the New Memory Access Analysis Feature of Intel® VTune<sup>™</sup> Amplifier XE

Kevin O'Leary, Software Technical Consulting Engineer; Dmitry Ryabtsev, Software Development Engineer; and Alexey Budankov, Software Development Engineer; Intel Corporation

How your application accesses memory can dramatically impact performance. It's not enough to parallelize your application by adding threads and **vectorization**. Memory bandwidth is just as important, but is often not as well understood by software developers. Tools that help minimize memory latency and increase bandwidth can help developers pinpoint performance bottlenecks and diagnose their causes.

Today's modern processors have many different types of memory accesses. For example, the latency of an L1 cache hit is vastly different from the latency of an access that misses all of your

memory caches and needs to access DRAM. There are additional complexities brought about by non-uniform memory access (NUMA) architectures.

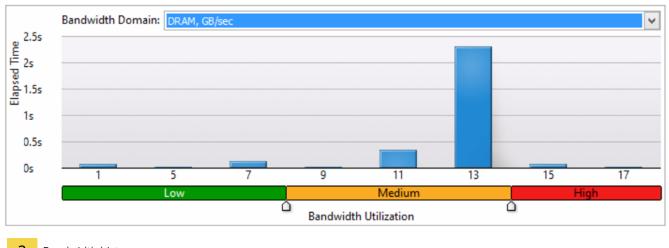

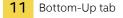

Intel<sup>®</sup> VTune<sup>™</sup> Amplifier XE is a performance profiler that has many features you can use to analyze memory accesses. These features are contained in the new Memory Access analysis type, which lets you:

- Detect performance problems by memory hierarchy (e.g., L1-, L2-, LLC-, DRAM-bound).

- **Track memory objects** and attribute the latency these objects cause to their appropriate code and data structures.

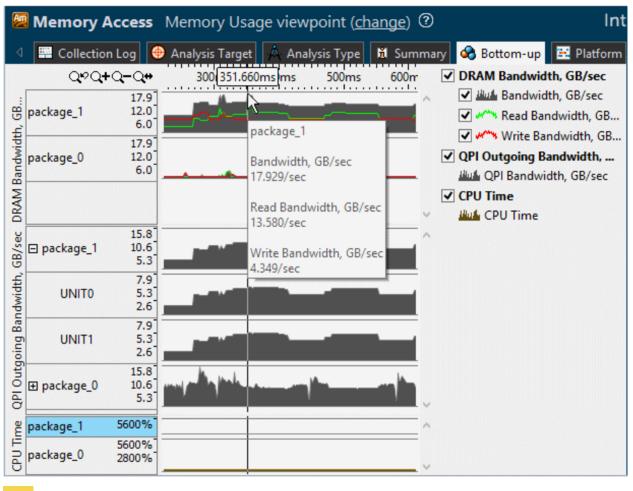

- Analyze bandwidth-limited accesses (including DRAM and Intel® QuickPath Interconnect [Intel® QPI] bandwidth) and quickly see graphs and histograms of your DRAM and QPI that show you bandwidth over the timeline of your program.

- Identify NUMA-related issues contributing to performance problems.

This article provides an overview of the new Memory Access feature and how it can help solve several tough memory problems and greatly increase an application's performance.

### **Overview**

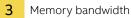

To access Intel VTune Amplifier's Memory Access feature, click on the new "Memory Access" analysis type, and then click "Start" (**Figure 1**).

| A A A A                                                                                       | Memory Access Copy                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Algorithm Analysis</li> <li>A Basic Hotspots</li> <li>A Advanced Hotspots</li> </ul> | Measure a set of metrics to identify memory access related issues<br>(for example, specific for NUMA architectures). This analysis type is<br>based on the hardware event-based sampling collection. <u>Learn more</u><br>(F1) |

| Å Concurrency<br>Å Locks and Waits<br>▽ Microarchitecture Analy:                              | CPU sampling interval, ms: 1<br>☑ Analyze memory objects                                                                                                                                                                       |

| A General Exploration<br>A Memory Access                                                      | Minimal memory object size to track, in bytes: 1024                                                                                                                                                                            |